# Alma Mater Studiorum Università di Bologna Archivio istituzionale della ricerca

Gate Reliability of p-GaN Power HEMTs Under Pulsed Stress Condition

This is the final peer-reviewed author's accepted manuscript (postprint) of the following publication:

Published Version:

Millesimo, M., Bakeroot, B., Borga, M., Posthuma, N., Decoutere, S., Sangiorgi, E., et al. (2022). Gate Reliability of p-GaN Power HEMTs Under Pulsed Stress Condition. Institute of Electrical and Electronics Engineers Inc. [10.1109/IRPS48227.2022.9764592].

Availability: This version is available at: https://hdl.handle.net/11585/895283 since: 2022-10-03

Published:

DOI: http://doi.org/10.1109/IRPS48227.2022.9764592

Terms of use:

Some rights reserved. The terms and conditions for the reuse of this version of the manuscript are specified in the publishing policy. For all terms of use and more information see the publisher's website.

This item was downloaded from IRIS Università di Bologna (https://cris.unibo.it/). When citing, please refer to the published version.

(Article begins on next page)

This is the post-print peer-review accepted manuscript of:

M. Millesimo et al. " Gate Reliability of p-GaN Power HEMTs Under Pulsed Stress Condition" in *IEEE International Reliability Physics Symposium Proceedings 2022,* No. 21725964, March 2022, DOI: 10.1109/IRPS48227.2022.9764592.

The published version is available online at:

https://ieeexplore-ieee-org.ezproxy.unibo.it/document/9764592

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

# Gate Reliability of p-GaN Power HEMTs Under Pulsed Stress Condition

M. Millesimo<sup>1</sup>, B. Bakeroot<sup>2</sup>, M. Borga<sup>3</sup>, N. Posthuma<sup>3</sup>, S. Decoutere<sup>3</sup>, E. Sangiorgi<sup>1</sup>, C. Fiegna<sup>1</sup>, and A. N. Tallarico<sup>1</sup>

1. ARCES-DEI, University of Bologna, Cesena, Italy, e-mail: maurizio.millesimo2@unibo.it

2. Centre for Microsystems Technology, imec and Ghent University, Technologiepark 126, 9052 Ghent, Belgium

3. imec - Kapeldreef 75, 3001 Leuven, Belgium

*Abstract*—A combined experimental/simulation analysis has been performed to study the gate reliability of GaN-HEMTs with p-type gate under pulse stress conditions. Results show that the time-dependent gate breakdown (TDGB) can be determined by two factors: i) the total ON-time during which the device is subjected to a positive gate bias before the failure; ii) the number of pulses, hence the number of switching phases from OFF- to ON-State and vice versa. The severity of the degradation ascribed to transition phases depends on the OFFtime (toFF) and transition time (trR = tRISE = tFALL). In particular, the shorter toFF and trR, the higher the Schottky junction voltage drop and the current peak during the switching phase, respectively. The higher voltage drop is ascribed to the semifloating potential of the p-GaN layer.

*Index Terms*—Gallium Nitride, HEMTs Reliability, p-GaN Gate, Pulsed Gate Stress, TCAD Modeling.

#### I. INTRODUCTION

To date, GaN-based power high electron mobility transistors (HEMTs) emerged as one of the most suitable technology for high-voltage and high-power applications due to their capability to operate at relatively high frequency with higher efficiency when compared with their Silicon-based counterpart [1]-[4]. Among all the solutions for normally-OFF operation, a Magnesium-doped (p-type) GaN layer placed between a gate metal and an AlGaN barrier layer, results to be one of the best choice from performance, stability and cost point of view [5]-[8].

In a typical switching application, e.g. in a power converter, the gate of such transistors is repeatedly switched,

This activity was funded under project iRel40. iRel40 is a European co-funded innovation project that has been granted by the ECSEL Joint Undertaking (JU) under grant agreement No 876659. The funding of the project comes from the Horizon 2020 research programme and participating countries. National funding is provided by Germany, including the Free States of Saxony and Thuringia, Austria, Belgium, Finland, France, Italy, the Netherlands, Slovakia, Spain, Sweden, and Turkey. This project is co-funded by the Ministry of Economic Development in Italy. at relatively high frequency, between high (ON-state) and low voltage values (OFF-state). Therefore, reliability analysis under pulsed gate conditions is of paramount importance.

Although, the metal/p-GaN Schottky contact effectively limits the gate leakage [9], the semi-floating p-GaN layer potential can lead to charging/discharging processes inside the metal/p-GaN/AlGaN/GaN epi-stack, causing critical reliability and electrical performance degradation concerns under pulsed conditions.

Many papers reported how fast transient and/or pulsed stress/characterization may induce threshold voltage shifts ( $\Delta V_{TH}$ ) [10]-[16]. In [13], He et al. showed that fast-dynamic forward gate stress induces frequency dependent positive  $\Delta V_{TH}$ . Such behavior has been attributed to carrier injection/emission in/from the p-GaN layer or the AlGaN barrier layer.

Tang et al. [14] observed positive threshold voltage shift ascribed to trapping of electrons, coming from the 2DEG through the AlGaN barrier, in the p-GaN layer. The latter becomes negatively charged until the electron de-traps after a certain relaxation time under zero bias condition.

In [15], a fully recoverable  $\Delta V_{TH}$  hysteresis under fast sweeping characterization has been reported. In particular, the sweeping time was found to be crucial for threshold voltage shift, i.e., the longer the sweeping time the higher the positive  $V_{TH}$  shift. Recently, in [16] has been proposed an accurate TCAD modeling of such phenomena, attributing the dynamic  $V_{TH}$  shift to time dependent charging/discharging processes in the floating p-GaN layer, which are ruled by the balance of both the Schottky diode (metal/p-GaN) and p-i-n diode (p-GaN/AlGaN/GaN) leakage currents.

While the time-dependent gate breakdown (TDGB) under static stress condition has been largely analyzed for this technology [17]-[22], only a few papers about the case of pulsed gate stress were reported in the literature so far.

To the best of our knowledge, only a frequency-dependent gate degradation under pulsed stress, up to 100 kHz, has been studied in [23], reporting a weak frequency dependency of the gate Mean Time-to-Failure (MTTF).

In this paper, the time-dependent gate breakdown under dynamic stress condition has been investigated for higher frequencies (up to 3.3 MHz). More specificly, this work aims to investigate which are the AC signal features (e.g. ON-time, OFF-time, rise/fall time, etc.), applied to the gate terminal, causing irreversible failure. Experimental results combined to TCAD simulations highlight reliability aspects which could not be identified by DC stress analysis.

## II. DEVICE UNDER TEST AND ANALYSIS DETAILS

Devices under test (DUTs) are p-GaN gate HEMTs grown by metalorganic chemical vapor deposition (MOCVD) on a 200mm GaN-on-Si substrate by imec. The epi-stack consists of a 200-nm AlN nucleation layer, a 1.65- $\mu$ m (Al) GaN superlattice layer, a 1- $\mu$ m C-doped GaN back barrier, a 200-nm undoped GaN channel layer, a 16-nm thick AlGaN barrier with 23.5% Aluminum (Al) content, and a 70-nm Mg-doped p-GaN layer with a dopant concentration of 3 × 10<sup>-19</sup> cm<sup>-3</sup>. For additional process details see [8].

The considered structures, realized for gate reliability studies, feature equal gate-to-source and gate-to-drain distance ( $L_{GS} = L_{GD}$ ) of 1.25 µm. The gate width ( $W_G$ ) and length ( $L_G$ ) are 10 µm and 0.5 µm, respectively.

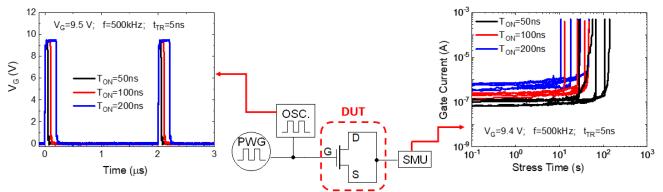

The time-dependent gate breakdown analyses under pulsed stress condition have been carried out by applying consecutive square-wave at the gate contact by means of a Pulse Wave Generator (PWG), while the source and drain contacts are both forced to 0 V through a Source Measure Unit (SMU), as shown in the schematic reported in Fig. 1. The SMU monitors the leakage current (Gate Current) in order to indirectly detect the gate breakdown. Furthermore, an oscilloscope has been connected, together with the PWG, at the gate contact to monitor the applied signals during the tests. Thanks to appropriate 50 Ohm impedance matching and control of parasitics, the measured waveforms do not show any significant voltage overshoot/spike in the considered frequency ranges.

The Time to Failure (TTF) is defined as the time at which the current abruptly increases over a certain value (1 mA in this work). The experimental results are analyzed in terms of: a) mean time-to-failure (MTTF) extrapolated with an arithmetic average on the time-to-breakdown of 7-15 devices; b) mean number of pulses necessary to reach the breakdown, defined as: Mean N° of Pulses = MTTF/Period; c) mean Total ON-Time, i.e. the total time in which the device is in ON-State before the breakdown (Mean N° of Pulses\*T<sub>ON</sub>).

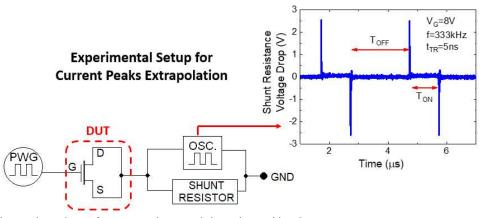

To sense the current peaks at the transition phases, an additional experimental setup has been employed. As before, a square waveform is applied at the gate contact while the drain and the source contacts are shorted. Here, the current flows through a shunt/sensing resistor and the voltage drop across it is monitored by means of a high-resolution oscilloscope (see Fig. 2).

For the scope of this work, the applied square-waves at the gate terminal feature different ON-Time ( $t_{ON}$ ), OFF-time ( $t_{OFF}$ ) and rise/fall time (or transition time  $t_{TR}$ ), while the amplitude ( $V_G$ ) is 9.4 V and 8V for the TTF and current

Fig. 1. Schematic of the experimental setup for time-dependent gate breakdown pulsed analysis.

Fig. 2. Schematic of the experimental setup for current peaks extrapolation at the transition phases.

peaks extrapolation, respectively. The temperature is fixed at 150° C for all the experiments.

The experimental results are supported by TCAD simulations. In the case of HEMTs with p-type gate, the modeling of the gate leakage is of paramount importance, playing an important role on the devices' threshold voltage [24]. Specifically, the balancing between the metal/p-GaN Schottky junction and p-GaN/AlGaN/GaN (p-i-n) junction leakage components determines the charging state of the semi-floating p-GaN layer. As a matter of fact, nonlocal tunneling models [25] in combination with thermionic emission contributions have been adopted and defined for both junctions. Hole tunneling, reproducing the hole injection from the metal to p-GaN valence band, has been activated and calibrated at the Schottky gate contact, whereas nonlocal trap assisted tunneling (TAT) has been used to model the leakage current through the AlGaN barrier. Such TAT is allowed for both electrons and holes coming from 2DEG (two-dimensional electron gas) and 2DHG (two-dimensional hole gas), respectively, and includes both inelastic phononassisted and elastic processes. More details about the adopted models and calibration can be found in [16].

#### III. RESULTS AND DISCUSSION

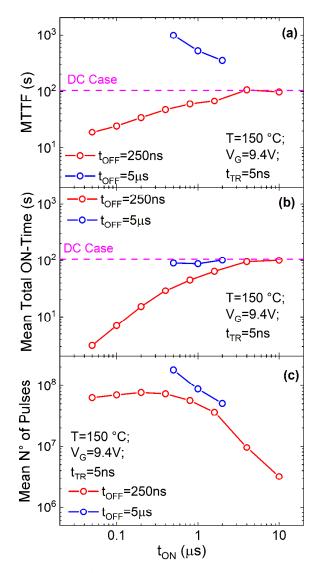

Fig. 3(a) shows the mean time-to-failure as a function of  $t_{ON}$  for two fixed  $t_{OFF}$  values, 250 ns and 5  $\mu$ s. In the first case, the MTTF increases with  $t_{ON}$ , whereas an opposite trend is observed with  $t_{OFF} = 5 \ \mu$ s. For a better understanding, the mean Total ON-Time is compared with the DC case in Fig. 3(b). DC condition represents the mean time-to-failure extrapolated by typical Constant Voltage Stress (CVS) tests at 9.4 V, i.e. the same value of the square-wave amplitude used for pulsed stress test.

From Fig. 3(b) emerges that, in the case of  $t_{OFF} = 250$  ns, for  $t_{ON} \le 2 \ \mu s$  the mean total ON-time is shorter than the DC case. On the other hand, for  $t_{ON} > 2 \mu s$ , as well as for longer  $t_{OFF}$  (5 µs), the mean total ON-time features values close to that one extrapolated by CVS tests. From these preliminary results, it can be hypothesized that dynamic gate stress, hence the transition phases, introduces degradation effects in addition to the total time during which the applied gate voltage is at the higher value. This is supported by Fig. 3(c), showing that for relatively short ON- and OFF-time (< 1 µs and 250 ns, respectively), the mean N° of pulses is roughly constant independently of t<sub>ON</sub>, suggesting that the number of transition phases is determining the TDGB. On the contrary, by further increasing  $t_{ON}$  (> 2  $\mu$ s), the degradation ascribed to Total ON-Time starts to be dominant, leading to a gate TTF with a reduced N° of pulses. As a result, the degradation induced by the transition phase is reduced as well, giving rise to a Total ON-Time to failure equal to DC-MTTF (Fig. 3b). Same behavior is observed with a  $t_{OFF} = 5 \ \mu s$ , suggesting that a longer t<sub>OFF</sub> is weakening the degrading effect of the transition phase, in fact, once again, the Total ON-time to failure equals the DC case (Fig. 3b).

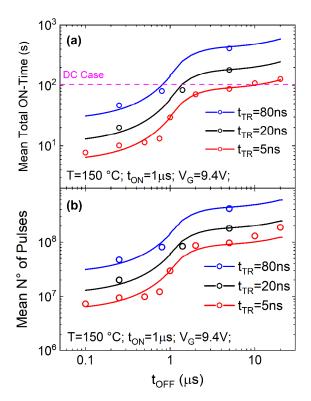

In order to understand which factors impact the transition phase degradation effect, dynamic time-dependent gate breakdown tests with different OFF-time (ranging from 100 ns to 20  $\mu$ s) and transition time (5 ns, 20 ns and 80 ns) have been performed at fixed t<sub>ON</sub> =1  $\mu$ s.

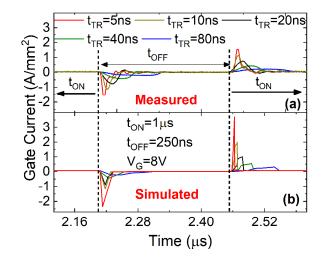

Fig. 4(a) shows that the mean Total ON-time depends on both  $t_{OFF}$  and  $t_{TR}$ . In particular, the shorter  $t_{TR}$ , the shorter the mean Total ON-Time to failure. To explain such trend, the current has been monitored with experimental setup described in the previous section (Fig. 2), by varying the transition time (from 5 ns to 80 ns) and by fixing  $t_{ON} = 1 \ \mu s$ ,  $t_{OFF} = 250 \ ns$ and  $V_G = 8 \ V$ . Fig. 5(a) shows that the current peaks occurring during the rising and falling phases are strongly impacted by the transition time. In particular, the shorter the transition time, the higher and tighter the current peaks at

Fig. 3. ON-Time dependency of the Mean Time-to-Failure (a), Mean Total ON-Time to Failure (b) and Mean Number of Pulses (c) with two fixed OFF time, i.e., 250 ns (red) and 5  $\mu$ s (blue). Results of time-dependent gate breakdown tests with V<sub>G</sub> = 9.4 V, T = 150 °C and t<sub>TR</sub> = 5 ns. Each experimental data point is the average over 7-15 devices.

Fig. 4. OFF-Time dependency of the Mean Total ON-Time (a) and Mean Number of Pulses (b) with fixed ON-time (1  $\mu$ s). Results of time dependent gate breakdown tests with V<sub>G</sub> = 9.4 V, T = 150 °C and three different t<sub>TR</sub> (5 ns, 20 ns and 80 ns). Each experimental data point is the average over 7-15 devices.

both rise and fall switching phases. As a result, the faster is the transition phase the stronger is the degradation effect induced by the current spikes, possibly responsible of the gate time-to-failure reduction. A good agreement has been found with the TCAD-simulated gate current (Fig. 5b), reproducing the same  $t_{TR}$  dependency and confirming that the current overshoots are not introduced by the stray inductance of the test circuit but by the gate stack structure itself.

In addition to  $t_{TR}$  dependency, results show that the degradation effect associated to the transition phase is effectively reduced also increasing  $t_{OFF}$ . This is confirmed by Fig. 4(b), showing that the N° of pulses that the device can handle before the gate breakdown increases with both  $t_{OFF}$  and  $t_{TR}$ .

Moreover, it is worth noting that for longer  $t_{TR}$  and  $t_{OFF}$ , the mean Total ON-time is longer than DC-MTTF (Fig. 4(a)). This might be possible if the defects produced during the ON-time are partially recovered during the OFF-time, assuming the degradation due to switching phases is negligible thanks to long  $t_{TR}$  (relatively low leakage current peak). From percolation theory [26]-[28], when a relatively high electric field is applied to a defective region, new defects/traps are created in addition to pre-existent ones. Once a critical number of defects forms in a specific location, a percolation path, inducing layer/device breakdown, is created. Such processes are time dependent. Unlike DC case, under pulsed stress condition the time necessary to reach the failure (i.e.,

Fig. 5. Measured (a) and simulated (b) gate current with  $t_{ON} = 1 \ \mu s$  and  $t_{OFF} = 250 \ ns$  and different transition times.

the creation of enough new defects) might be longer since the stress time is interrupted (OFF-time); this relaxation period possibly induces a partial recovery of the failure processes.

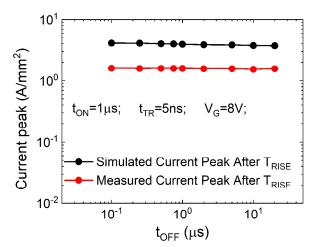

The  $t_{OFF}$  dependency cannot be explained by the current peak during the switching phase since, as confirmed by experiments and TCAD simulations, it does not change by varying the OFF-time (Fig. 6), even if the gate reliability is strongly influenced by  $t_{OFF}$  as shown in Fig. 4.

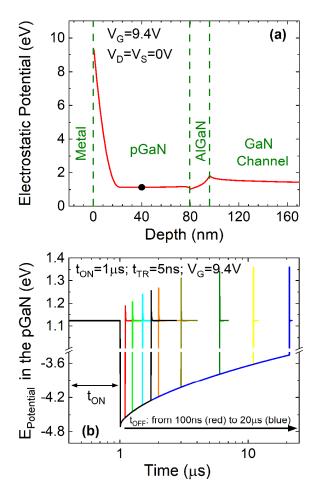

Thanks to TCAD simulations, the electrostatic potential has been monitored by varying  $t_{OFF}$  in the middle of the semifloating p-GaN layer (at 40 nm away from gate metal and pGaN/AlGaN interface), in a region where the carrier density is constant since it is far away from the Schottky depletion region and the 2DHG layer (Fig. 7a). In Fig. 7 (b), it can be observed that after the transition from ON- to OFF-state (fall time) the p-GaN potential is at the same level whatever the  $t_{OFF}$  is. During the OFF-state phase (i.e.  $V_G = 0$  V) such potential changes/recovers and then, when the device turn-on

Fig. 6. OFF-Time dependency of the measured (red) and simulated (black) current peak at the switching phase.

Fig. 7. Simulated electrostatic potential along the device at  $V_G = 9.4 V$  and  $V_S = V_D = 0 V$  (a). TCAD simulation of the electrostatic potential monitored in the semi-floating p-GaN layer with different OFF-Time (b).

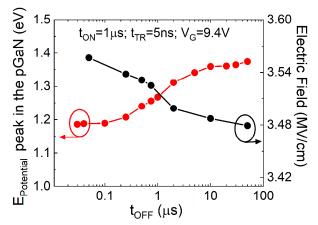

occurs, it shows a peak after the rise time. Such phenomenon is ruled by the recovery time, i.e. the longer the OFF-time the higher the height of the potential peak, inducing a lower Schottky junction voltage drop, hence a lower electric field across the Schottky depletion region (see Fig. 8). This explains the reason why a longer  $t_{OFF}$  leads to a longer MTTF.

Fig. 8 reports the Electrostatic Potential peaks after the rise time and the correspondent Electric Field across the Schottky depletion region. It is worth noticing that the observed dependency on the  $t_{OFF}$  is similar to the one shown in the case of mean Total ON-time and mean N° of pulses (Fig. 4).

## IV. CONCLUSION

An in-depth analysis of TDGB of p-GaN HEMTs under pulsed stress condition at 150 ° C has been proposed. The gate time-to-failure has been investigated by means of applied consecutive square-waves, featuring different ON-time, OFF-time and rise/fall time, supported by transient current sensing and TCAD simulations.

Two main factors determine the time-dependent gate breakdown of GaN-HEMTs with p-type gate under pulsed

Fig. 8. OFF-Time dependency of the Electrostatic potential peaks at the transition from OFF- to ON-State (just after  $t_{RISE}$ ) and corresponding mean electric field evaluated across the depletion region of the Schottky junction.

stress conditions: the switching phase (number of applied pulses) and the time in which the device is kept in ON-State, plus a possible recovery mechanism occurring during the  $t_{OFF}$ .

The amount of degradation coming from the switching phase depends on both  $t_{OFF}$  and  $t_{TR}$ . The latter is responsible of altering the amplitude of the current peak during the switching phase. The longer the  $t_{TR}$ , the lower the amplitude of such current spikes, the longer the TTF. A good agreement between simulations and experiments has been found.

The OFF-time dependency is ascribed to electrostatic potential in the semi-floating p-GaN layer at the switching phase (from OFF to ON). From TCAD simulations, it emerged that the potential peak increases with the OFF-time leading to a lower voltage drop, hence electric field, on the Schottky depletion region. The simulated p-GaN potential and the Mean Total ON-Time show similar trends with t<sub>OFF</sub>.

In conclusion, it can be stated that a too short  $t_{TR}$  and  $t_{OFF}$  gives rise to a shorter time-dependent gate breakdown compared to DC stress condition.

#### REFERENCES

- K. J. Chen *et al.*, "GaN-on-Si Power Technology: Devices and Applications," in *IEEE Transactions on Electron Devices*, vol. 64, no. 3, pp. 779-795, March 2017, doi: 10.1109/TED.2017.2657579.

- [2] O. Ambacher et al.,"Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures", Journal of Applied Physics 85, 3222-3233 (1999).

- [3] J. Millán, P. Godignon, X. Perpiñà, A. Pérez-Tomás and J. Rebollo, "A Survey of Wide Bandgap Power Semiconductor Devices," in *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2155-2163, May 2014.

- [4] R. Rupp, T. Laska, O. Häberlen and M. Treu, "Application specific trade-offs for WBG SiC, GaN and high-end Si power switch technologies," 2014 IEEE International Electron Devices Meeting, 2014, pp. 2.3.1-2.3.4, doi: 10.1109/IEDM.2014.7046965.

- [5] D. Marcon, M. Van Hove, B. De Jaeger, N. Posthuma, D. Wellekens, S. You, X. Kang, Tian-Li Wu, M. Willems, S. Stoffels, and S. Decoutere "Direct comparison of GaN-based e-mode architectures (recessed MISHEMT and p-GaN HEMTs) processed on 200mm GaN-on-Si with Au-free technology", Proc. SPIE 9363, Gallium Nitride Materials and Devices X, 936311, 2015.

- [6] G. Greco, F. Iucolano, F. Roccaforte, "Review of technology for normally-off HEMTs with p-GaN gate", Materials Science in Semiconductor Processing, vol. 78, pp. 96-106 (2018).

- [7] C. S. Suh and U. K. Mishra, "P-GaN/AlGaN/AlN/GaN enhancementmode field effect transistor," U.S. Patent 20 080 296 618 A1, 2008.

- [8] N. E. Posthuma et al., "An industry-ready 200 mm p-GaN E-mode GaN- on-Si power technology," 2018 IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2018, pp. 284-287.

- [9] I. Hwang et al., "p-GaN Gate HEMTs With Tungsten Gate Metal for High Threshold Voltage and Low Gate Current," in *IEEE Electron Device Letters*, vol. 34, no. 2, pp. 202-204, Feb. 2013, doi: 10.1109/LED.2012.2230312.

- [10] L. Sayadi, G. Iannaccone, S. Sicre, O. Häberlen and G. Curatola, "Threshold Voltage Instability in p-GaN Gate AlGaN/GaN HFETs," in *IEEE Transactions on Electron Devices*, vol. 65, no. 6, pp. 2454-2460, June 2018, doi: 10.1109/TED.2018.2828702.

- [11] Y. Shi et al., "Carrier transport mechanisms underlying the bidirectional VTH shift in p-GaN gate HEMTs under forward gate stress," *IEEE Trans. Electron Devices*, vol. 66, no. 2, pp. 876–882, Feb. 2019.

- [12] J. Wei et al., "Charge Storage Mechanism of Drain Induced Dynamic Threshold Voltage Shift in \${p}\$ -GaN Gate HEMTs," in *IEEE Electron Device Letters*, vol. 40, no. 4, pp. 526-529, April 2019, doi: 10.1109/LED.2019.2900154.

- [13] J. He, G. Tang, and K. J. Chen, "VTH instability of p-GaN gate HEMTs under static and dynamic gate stress," *IEEE Electron Device Lett.*, vol. 39, no. 10, pp. 1576–1579, Oct. 2018.

- [14] X. Tang et al., "Demonstration of electron/hole injections in the gate of p-GaN/AlGaN/GaN power transistors and their effect on device dynamic performance," in Proc. 31st Int. Symp. Power Semiconductor Devices ICs (ISPSD), May 2019, pp. 415–418.

- [15] X. Li et al., "Observation of Dynamic V<sub>TH</sub> of p-GaN Gate HEMTs by Fast Sweeping Characterization," in *IEEE Electron Device Letters*, vol. 41, no. 4, pp. 577-580, April 2020, doi: 10.1109/LED.2020.2972971.

- [16] A. N. Tallarico *et al.*, "TCAD Modeling of the Dynamic  $\Delta V_{TH}$ Hysteresis Under Fast Sweeping Characterization in p-GaN Gate HEMTs," in *IEEE Transactions on Electron Devices*, vol. 69, no. 2, pp. 507-513, Feb. 2022, doi: 10.1109/TED.2021.3134928.

- [17] T.-L. Wu et al., "Forward bias gate breakdown mechanism in enhancement-mode p-GaN gate AlGaN/GaN high-electron mobility transistors," IEEE Electron Device Lett., vol. 36, no. 10, pp. 1001– 1003, Oct. 2015. doi: 10.1109/LED.2015.2465137.

- [18] I. Rossetto et al., "Time-dependent failure of GaN-on-Si power HEMTs with p-GaN gate," IEEE Trans. Electron Devices, vol. 63, no. 6, pp. 2334–2339, Jun. 2016. doi: 10.1109/TED.2016.2553721.

- [19] M. Meneghini et al., "Degradation of GaN-HEMTs with p-GaN gate: Dependence on temperature and on geometry," in Proc. IRPS, Apr. 2017, pp. 4B-5.1–4B-5.5. doi: 10.1109/IRPS.2017. 7936311.

- [20] S. Stoffels et al., "Failure mode for p-GaN gates under forward gate stress with varying Mg concentration," in Proc. IRPS, Apr. 2017, pp. 4B-4.1–4B-4.9. doi: 10.1109/IRPS.2017.7936310.

- [21] M. Millesimo et al., "High-Temperature Time-Dependent Gate Breakdown of p-GaN HEMTs," in *IEEE Transactions on Electron Devices*, vol. 68, no. 11, pp. 5701-5706, Nov. 2021, doi: 10.1109/TED.2021.3111144.

- [22] A. N. Tallarico *et al.*, "Gate Reliability of p-GaN HEMT With Gate Metal Retraction," in *IEEE Transactions on Electron Devices*, vol. 66, no. 11, pp. 4829-4835, Nov. 2019, doi: 10.1109/TED.2019.2938598.

- [23] J. He, J. Wei, S. Yang, Y. Wang, K. Zhong and K. J. Chen, "Frequency- and Temperature-Dependent Gate Reliability of Schottky-Type p-GaN Gate HEMTs," in *IEEE Transactions on Electron Devices*, vol. 66, no. 8, pp. 3453-3458, Aug. 2019, doi: 10.1109/TED.2019.2924675.

- [24] B. Bakeroot, S. Stoffels, N. Posthuma, D. Wellekens and S. Decoutere, "Trading Off between Threshold Voltage and Subthreshold Slope in AlGaN/GaN HEMTs with a p-GaN Gate," 2019 31st International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2019, pp. 419-422, doi: 10.1109/ISPSD.2019.8757629.

- [25] Sentaurus-Device U.G. V. P-2019.03, Synopsys Inc., Mountain View, CA, USA, 2019.

- [26] J. Suñé, I. Placencia, N. Barniol, E. Farrés, F. Martín, and X. Aymerich, "On the breakdown statistics of very thin SiO2 films," Thin Solid Films, vol. 185, no. 2, pp. 347–362, Mar. 1990.

- [27] S. W. Kenkel and J. P. Straley, "Percolation Theory of Nonlinear Circuit Elements", Phys. Rev. Lett., vol. 49, pp. 767-770, (1982).

- [28] M. Houssa, T. Nigam, P.W. Mertens, and M. M. Heyns, "Soft breakdown in ultrathin gate oxides: Correlation with the percolation theory of nonlinear conductors", Appl. Phys. Lett. 73, 514-516 (1998)