# Alma Mater Studiorum Università di Bologna Archivio istituzionale della ricerca

Understanding the impact of split-gate LDMOS transistors: Analysis of performance and hot-carrier-induced degradation

This is the final peer-reviewed author's accepted manuscript (postprint) of the following publication:

### Published Version:

Magnone, P., Tallarico, A., Pistollato, S., Depetro, R., Croce, G. (2021). Understanding the impact of split-gate LDMOS transistors: Analysis of performance and hot-carrier-induced degradation. SOLID-STATE ELECTRONICS, 185, 1-4 [10.1016/j.sse.2021.108068].

Availability:

This version is available at: https://hdl.handle.net/11585/833396 since: 2021-11-25

Published:

DOI: http://doi.org/10.1016/j.sse.2021.108068

Terms of use:

Some rights reserved. The terms and conditions for the reuse of this version of the manuscript are specified in the publishing policy. For all terms of use and more information see the publisher's website.

This item was downloaded from IRIS Università di Bologna (https://cris.unibo.it/). When citing, please refer to the published version.

(Article begins on next page)

This is the post-print version of the manuscript:

Understanding the impact of split-gate LDMOS transistors: analysis of performance and hot-carrier-induced degradation.

The final published version is available online at:

https://doi.org/10.1016/j.sse.2021.108068

© [2021]. This manuscript version is made available under the Creative Commons Attribution-NonCommercial-NoDerivs (CC BY-NC-ND) 4.0 International License (http://creativecommons.org/licenses/by-nc-nd/4.0/)

# Understanding the impact of split-gate LDMOS transistors: analysis of performance and hot-carrier-induced degradation

P. Magnone<sup>1</sup>, A. N. Tallarico<sup>2</sup>, S. Pistollato<sup>1</sup>, R. Depetro<sup>3</sup>, G. Croce<sup>3</sup>

<sup>1</sup>DTG, University of Padova, Vicenza, Italy

<sup>2</sup>ARCES and DEI, University of Bologna, Cesena, Italy

<sup>3</sup>Technology R/D, STMicroelectronics, Agrate Brianza, Italy

E-mail address of corresponding author: paolo.magnone@unipd.it

#### **Abstract**

In this paper a split-gate LDMOS transistor is investigated. A dedicated terminal, namely split-gate, is introduced in order to control the field plate region separately with respect to the channel region. The performances of the device, in terms of on-resistance, breakdown voltage and capacitances, are compared with those of a conventional device. The hot-carrier-induced degradation of the device is also investigated, highlighting the influence of the split-gate voltage. This work allows identifying a tradeoff between the performance and reliability of the component, which is controlled by the voltage applied to the split-gate terminal.

#### 1. Introduction

LDMOS transistor represents a suitable solution for integrated smart power applications. Its structure features an extended gate field-plate aimed at ensuring a good trade-off between performance and reliability. However, the relatively large gate area, hence the gate capacitance, may limit the dynamic performance of such devices. To mitigate this issue, a separate secondary gate can be considered for the field-plate region, namely split-gate LDMOS [1-4]. In high-frequency applications, the split-gate contact can be biased with a constant voltage, allowing to reduce the capacitance seen from the gate terminal.

Hot-carrier degradation (HCD) is a typical effect, limiting the lifetime of LDMOS transistors [5-7]. The large lateral electric field leads to the creation of interface traps in the drift region, hence degrading the on-resistance of the device.

This work aims at experimentally investigating the performance and the reliability of split-gate structures, which is described in section 2. In section 3, the influence of split-gate terminal voltage is analyzed, focusing on the on-resistance, breakdown voltage and capacitances of the device. The achieved results are compared with those of a conventional device, having a continuous gate contact. In section 4, hot-carrier degradation is investigated and the influence of a separate split-gate contact is evaluated. Finally, in section 5, the main achievements of the paper are summarized in the conclusions.

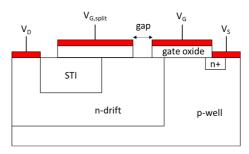

Fig. 1: Schematic view of an n-type split-gate LDMOS. A gap region (not in scale) is introduced in order to control by means of different terminals the channel region  $(V_G)$  and the field-plate region  $(V_{G,split})$ .

#### 2. Experimental

The device under test is a 40V n-type LDMOS integrated in 90 nm Bipolar-CMOS-DMOS (BCD) technology by STMicroelectronics. Two different topologies have been investigated: a "conventional" structure with a continuous gate contact; a "split-gate" structure with two accessible gate contacts, adopted to bias the channel and drift regions separately, as shown in the schematic view reported in Fig. 1.

Hot-carrier degradation is investigated by stressing the device with a constant large drain voltage, in the range between 40V and 50V, while the gate voltage is selected to maximize the impact ionization (ii), representing the worst-case scenario as it is periodically experienced during the switching processes in a power application. The quantification of wear-out is done by measuring the on-resistance in linear region ( $V_{DS} = 0.1V$  and  $V_{GS} = 5V$ ), while keeping the split-gate voltage  $V_{G,split}$  at 5V or to the constant value applied during the stress. Capacitancevoltage measurements are performed by applying a constant bias, between the considered terminals, and by superimposing a small signal with 50mV of amplitude and 1MHz of frequency. All the analyses are performed at room temperature.

IV and CV measurements are carried out by means of Agilent 4156B parameter analyzer and Agilent E4980A LCR meter, respectively.

# 3. Performance of fresh devices

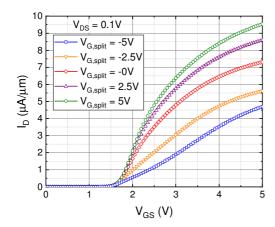

The transfer characteristics of the split-gate LDMOS are reported in Fig. 2 for different value of  $V_{G,split}$ . The

Fig. 2: Trans-characteristics at  $V_{DS}$ =100mV as a function of split-gate voltage.

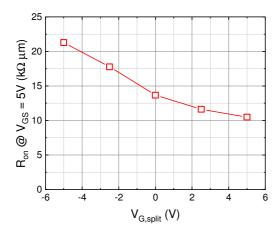

Fig. 3:  $R_{on}$  evaluated at  $V_{GS}$ =5V and  $V_{DS}$ =100mV as a function of split-gate voltage.

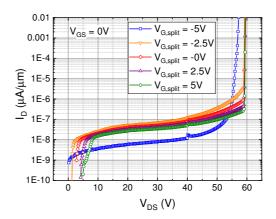

increase of  $V_{G,split}$  leads to an increase of the drain current and hence to a reduction of on-resistance,  $R_{on}$ , as shown in Fig. 3. This is due to the accumulation of electrons in the drift region. The breakdown voltage is evaluated in Fig. 4 as a function of  $V_{G,split}$ . In this case, the influence of split-gate voltage is limited, unless a large negative voltage is applied.

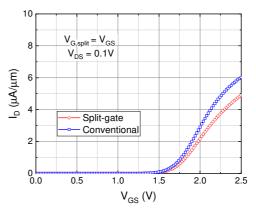

In Fig. 5, the transfer characteristics of a conventional device is compared with that of a split-gate device in which gate and split-gate terminals are short-circuited. A larger transconductance is observed in the case of conventional device. Therefore, R<sub>on</sub> is worsened in the case of split-gate structure because of the space region between the gate terminal and field-plate region.

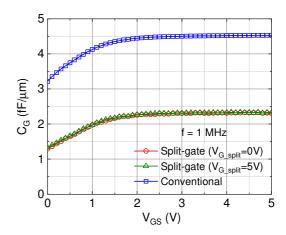

The gate-to-channel capacitance  $(C_G)$  is reported in Fig. 6. This capacitance represents the input capacitance of the device and is representative of the driving capability of the device. Hence, a lower value is desirable also to minimize driving losses. The

Fig. 4: Breakdown voltage at  $V_{GS}$ =0V as a function of splitgate voltage.

Fig. 5: Trans-characteristics at  $V_{DS}$ =100mV for split-gate device with  $V_{G,split}$ = $V_{GS}$  and a conventional device. The conventional device exhibits a larger transconductance, meaning that the presence of the gap negatively affects the transport within the channel.

Fig. 6: Gate-to-channel capacitance as a function of the gate voltage. Split-gate device allows significantly reducing the input capacitance.

capacitance is measured between gate and source/drain terminals. During the measurement the split-gate voltage is kept at a constant voltage (as reported in Fig. 6), while source, drain and substrate are biased to 0V. The split-gate device exhibits roughly half of the gate capacitance, compared to the conventional device. Moreover, this value is independent of the split-gate voltage.

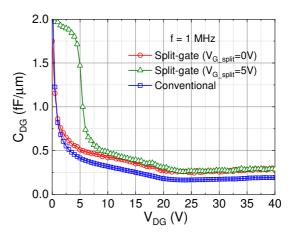

The drain-to-gate capacitance ( $C_{DG}$ ) is reported in Fig. 7. In the case of split-gate device, this capacitance includes both values of gate and split-gate regions. Source, substrate and gate terminals are biased to 0V, while the split-gate terminal is biased to 0V or 5V.  $C_{DG}$  is a relevant parameter affecting the switching performance of the device. From fig. 7, a similar value is observed for both device, while the biasing of the split-gate device leads to a shift of the CV curve. It is worth noting that, the small difference, between conventional and split-gate device, is comparable with the accuracy of the instrument and cannot be considered relevant.

### 4. Hot-carrier-induced degradation

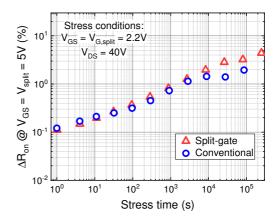

A comparison between HCD in split-gate and conventional devices, at  $V_{\rm DS}$ =40V, is reported in Fig. 8. The split-gate device is biased with  $V_{\rm G,split}$ = $V_{\rm GS}$ =2.2V, during both measure and stress phases, so that its behavior is as close as possible to the one of a conventional device. As a result, the observed  $R_{\rm on}$  degradation, evaluated at  $V_{\rm GS}$ = $V_{\rm G,split}$ =5V and  $V_{\rm DS}$ =0.1V, is very similar for both structures.

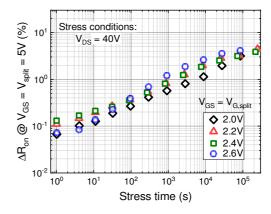

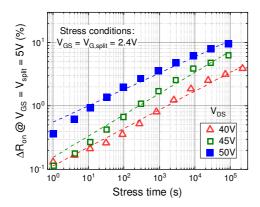

It is well known as the level of degradation due to HC is related to the impact ionization process. Therefore, it is important to estimate the value of the gate voltage at which the peak of ii occurs, typically with a gate over-drive voltage ranging between 0.5V and 1V [8]. Fig. 9 reports the analysis of  $R_{\text{on}}$ degradation as a function of the gate voltage, considering  $V_{DS}\!\!=\!\!40V$  and  $V_{G,split}\!\!=\!\!V_{GS}.$  HCD appears to be poorly dependent on the gate voltage in the range of V<sub>GS</sub> comprised between 2.0V and 2.6V. This result suggests that the peak of the electric field is localized close to the drain side, where the gate and split-gate voltages have a lower impact [1]. The dependence of the drain stress voltage on the on-resistance degradation is reported in Fig. 10. In order to predict the lifetime of the device, an increase of R<sub>on</sub> of 10% is considered as a failure criterion. By assuming a simple power law fitting for  $V_{DS}$ =40V (i.e. the nominal operating voltage of the device), a lifetime of 3.95·106 seconds, which is longer than 1000 hours, is achieved. However, this kind of fitting typically leads to an overestimation of the lifetime, while other models, accounting for the long-term

Fig. 7: Drain-to-Gate capacitance as a function of the drain voltage. Similar capacitance is observed in both conventional and split-gate structure.

Fig. 8: R<sub>on</sub> degradation after HC stress for split-gate and conventional structures.

Fig. 9:  $R_{on}$  degradation as a function of the gate voltage. Split-gate voltage is kept constant during this analysis.

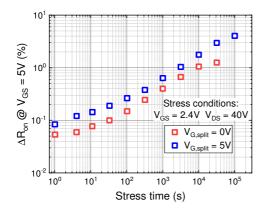

saturation effects [7], may be used to better predict the device lifetime. In Fig. 11, split-gate devices have been stressed with different  $V_{G,split}$ , ranging from 0 to 5V, and  $V_{DS}$ =40V. In this case  $R_{on}$  degradation is

Fig. 10: Ron degradation after HC stress for split-gate devices as function of the drain stress voltage.

Fig. 11:  $R_{on}$  degradation after HC stress ( $V_{DS} = 40V$ ) as a function of the split-gate voltage.

evaluated at the same  $V_{G,split}$  considered during the stress phase. By keeping  $V_{G,split}$ =0V, a lower degradation is observed. There are two possible explanations for this observation. i) When sensing  $R_{on}$  at  $V_{G,split}$ =0V, there is a lower electron density at the silicon/oxide interface of STI region with respect to the case  $V_{G,split}$ =5V. Hence, carriers transport can be less affected by interface state. ii) As reported in [1], considering a stress of  $V_{DS}$  = 40 V, the low-energy carriers (< 1eV), which flow confined to the silicon/oxide interface of the STI, play a fundamental role on the  $R_{on}$  degradation, since they repeatedly impinge the interface causing bonds breaking. By increasing  $V_{G,split}$ , their density increases as well [1], inducing a larger  $\Delta R_{on}$ .

# 4. Conclusions

In this work, a split-gate LDMOS structure has been investigated. With respect to a conventional device, the field-plate region is controlled with a separate terminal. Because of this solution, the input capacitance is significantly reduced (halved with respect to the conventional device) while the  $C_{\rm DG}$  is almost unchanged. The adoption of a large  $V_{\rm G,split}$  allows reducing the on-resistance of the device, because of

electrons accumulation in the drift region, while the impact on the breakdown voltage is limited. On the other hand, considering HC stress at  $V_{DS}$ =40V, lower values of  $V_{G,split}$  allow slightly reducing the  $R_{on}$  degradation. Hence, a tradeoff between performance and reliability can be identified.

In comparison to a conventional structure, the wearout of  $R_{\text{on}}$  during HC stress seems to be comparable in split-gate devices. However, the gate capacitance to be driven is smaller, allowing better high-frequency performance.

### Acknowledgements

This work was supported by H2020-EU ECSEL 737417: R3-PowerUP "300mm Pilot Line for Smart Power and Power Discrete".

The authors wish to thanks prof. Gerardin, University of Padova, for useful hints about experimental activity.

### References

- [1] F. Giuliano, P. Magnone, S. Pistollato, A. N. Tallarico, S. Reggiani, C. Fiegna, R. Depetro, Mattia Rossetti, G. Croce, «TCAD simulation of hot-carrier stress degradation in split-gate n-channel STI-LDMOS transistors» *Microelectron. Reliab.*, vol. 109 (2020), 1136433, 2020.

- [2] T. Mori; H. Fujii; S. Kubo; T. Ipposhi, «Investigation into HCl improvement by a split-recessed-gate structure in an STI-based nLDMOSFET», *Proc. of ISPSD* 2017, pp. 459-462, Sapport, Japan.

- [3] S. Liu, X. Ren, Y. Fang, W. Sun, W. Su, S. Ma, F. Lin, Y. Liu, G. Sun, «Hot-Carrier-Induced Degradations and Optimizations for Lateral DMOS Transistor With Multiple Floating Poly-Gate Field Plates», *IEEE Trans. Electron Devices*, vol. 64, no. 8, pp. 3275-3281, 2017.

- [4] S. Manzini, M Rossetti, «Electrical Characterization and Reliability of Split-Gate High-Voltage Transistors» *IEEE Trans. Device Mater. Rel.*, vol. 18, no. 2, pp. 279-283, 2018.

- [5] J. Chen, K.-S. Tian, S.-Y. Chen, K.-M. Wu, C. Liu, "Onresistance degradation induced by hot-carrier injection in LDMOS transistors with STI in the drift region,", *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 1071– 1073, 2008.

- [6] S. Reggiani, G. Barone, S. Poli, E. Gnani, A. Gnudi, G. Baccarani, M.-Y. Chuang, W. Tian, R. Wise, "TCAD simulation of hot-carrier and thermal degradation in STI-LDMOS transistors", *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 691–698, 2013.

- [7] A. N. Tallarico, S. Reggiani, R. Depetro, S. Manzini, A. M. Torti, G. Croce, E. Sangiorgi, C. Fiegna, "Hot-carrier degradation in power LDMOS: Drain bias dependence and lifetime evaluation", *IEEE Trans. Electron Devices*, vol. 65, no. 11, pp. 5195-5198, 2018.

- [8] A. N. Tallarico, S. Reggiani, P. Magnone, G. Croce, R. Depetro, P. Gattari, E. Sangiorgi, C. Fiegna, "Investigation of the hot carrier degradation in power LDMOS transistors with customized thick oxide", *Microelectron. Reliab.*, vol. 76-77, pp. 475-479, 2017.