The 9th International Conference on Power Electronics, Machines and Drives (PEMD 2018)

# Evaluation of DC-link voltage ripple in fivephase PWM voltage source inverters

eISSN 2051-3305 Received on 22nd June 2018 Accepted on 1st August 2018 E-First on 30th April 2019 doi: 10.1049/joe.2018.8102 www.ietdl.org

M. Vujacic¹ ⋈, M. Hammami¹, O. Dordevic², G. Grandi¹

<sup>1</sup>Department of Electrical, Electronic and Information Engineering, Alma Mater Studiorum University of Bologna, Italy

<sup>2</sup>Department of Electronics and Electrical Engineering, Liverpool John Moores University, UK

⋈ E-mail: marija.vujacic2@unibo.it

**Abstract:** This paper presents the analysis of the DC-link voltage switching ripple in five-phase PWM voltage source inverters with balanced load. The analysis is particularly important for the design and selection of a DC-link capacitor making it possible to meet desired electrical performance of the inverter system. Simple and practical equation for designing the DC-link capacitor is proposed relating the value of capacitance to the maximum value (peak-to-peak) of the DC-link voltage ripple. The amplitude of the DC-link voltage switching ripple is analytically derived as a function of modulation index, and the amplitude of the output current and phase angle. In order to show peak-to-peak voltage ripple distribution, different diagrams are introduced. Reference is made to continuous symmetric centred PWM modulation (i.e., space vector modulation SVM). In order to verify proposed developments, simulations have been carried out by Matlab/Simulink considering full range of modulation index and output phase angle.

#### 1 Introduction

In last decades, a large interest has been focused on multiphase variable-speed drives, due to many advantages obtained by joining multiphase motor and multiphase inverter. Compared to their traditional three-phase counterparts, main advantages are reduction of the stator current per phase without increasing the voltage per phase, reduction of the rotor harmonic currents, increased fault tolerance, and higher reliability. Also, multiphase motor drives offer the additional degrees of freedom which can be used for various purposes [1–3].

With the increase of interest in multiphase drives, many carrier-based (CB) and space vector (SV) PWM techniques have been developed for multiphase VSIs, enabling sinusoidal output voltage generation. The carrier-based PWM with common-mode injection, which leads to identical operation as SV PWM technique, is considered as the most practical and suitable control method. Recently, much effort has been directed towards development of SV PWM schemes in case of five-phase VSIs, since five-phase VSI is very common multiphase inverter configuration [4–8]. In general, due to the large number of space vectors, there is a lot of flexibility in choosing the proper combination of space vectors. By combining the utilisation of large and medium length neighbouring space vectors in an appropriate manner, sinusoidal output voltages are obtained without any low-order harmonics [9].

The analysis of the inverter characteristics at the input (DC-link) side is important for the selection of an appropriate DC-link capacitor. Critical performance specifications seem to be DC-link current ripple and voltage ripple since the DC-link capacitor is usually selected according to them. In general, voltage ripple can be significantly reduced by using the large capacitance. On the other side, the size of the DC-link capacitor should be kept as small as possible so high power density of the entire system can be achieved. It is shown in [10] that the input current ripple can be significantly reduced by increasing the phase number from three to five. However, the reduction is not significant when the phase number is more than nine.

In order to achieve an optimum minimisation of the DC-link capacitor, some studies are done and are mostly based on the Fourier analysis (harmonics) and RMS calculations of the input current and voltage characteristics. With reference to three-phase voltage source PWM inverters, the RMS value of the DC-link capacitor current, by using the time domain approach, is calculated

in [11, 12]. In [13, 14], the DC-link current spectra is described by a double Fourier series. In [15], the DC-link current and voltage ripple are calculated for inverters and rectifiers in hybrid electric vehicle (HEV) converter/inverter systems, operated by sinusoidal PWM and six-step modulation.

Regarding the five-phase case, the analysis related to the output current ripple peak-to-peak value has been presented in [16], and a detailed experimental verification has been provided in [17]. A similar idea is presented in [18], where the current ripple prediction method for multiphase PWM converters is proposed on the basis of the equivalent single-phase circuit. A study related to the input current and voltage ripple RMS has been reported in [19] for a five-phase VSI. DC current ripple is compared for different modulation techniques and it is shown that it is practically independent of it. However, the voltage ripple envelope and, in particular, the maximum value (peak-to-peak) of voltage ripple has not been examined yet.

A comprehensive analysis of the dc-link voltage ripple has been presented in [20] for single-phase H-bridge PWM inverters, considering both switching frequency and double-fundamental frequency components. Based on the voltage ripple requirements, simple expressions for designing the DC-link capacitor have been proposed. A thorough experimental verification is included in [21]. A similar investigation is done for three-phase PWM VSIs in [22], where the expression of peak-to-peak DC-link voltage ripple amplitude has been derived and different diagrams have been investigated in order to properly design the DC-link capacitor.

Here, the analysis of the DC-link voltage ripple in five-phase PWM voltage source inverter is presented, with the reference to continuous symmetric centred PWM modulation (i.e. SVM). The peak-to-peak DC voltage ripple amplitude is analytically determined over the fundamental period as a function of amplitude and phase angle of the output current, and the modulation index. In order to show the behaviour of the peak-to-peak DC voltage ripple amplitude in the fundamental period for full range of modulation index and output phase angle, the normalised function is considered. Maximum of the peak-to-peak voltage ripple amplitude is determined as a function of modulation index. Based on the analysis of DC-link components, simple and effective analytical expression for calculating the DC-link capacitance is obtained. The simulations are carried out by Matlab/Simulink to identify the effectiveness of the proposed theoretical developments.

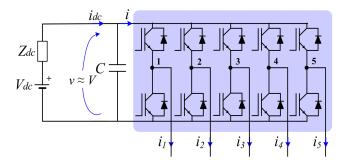

Fig. 1 Circuit scheme of the considered five-phase VSI

### 2 Basic inverter equations

#### 2.1 System configuration

Fig. 1 presents the circuit topology of a five-phase VSI with balanced passive or motor-load. The input DC voltage ( $V_{\rm dc}$ ) is regarded as being constant. For PWM modulated inverter, by neglecting DC-link voltage oscillations and by considering only linear modulation range ( $v \approx V$ ), the inverter output voltages averaged over the switching period correspond to five-phase sinusoidal reference signals:

$$v_k^* = mV\cos\left(\vartheta - (k-1)\frac{2\pi}{5}\right), \ k = 1, 2, ..., 5$$

(1)

where  $\vartheta = \omega t$ ,  $\omega = 2\pi/T$  is the fundamental angular frequency, T is the fundamental period and m is the inverter modulation index. The modulation index is defined as a ratio between the desired amplitude of the fundamental output voltage,  $V_o$ , and the inverter dc-link voltage, V, i.e.  $m = V_o/V$ .

Considering sinusoidal PWM output voltages (1), in case of balanced load and neglecting the output current ripple, the corresponding five-phase output currents are assumed sinusoidal as well (2):

$$i_k = I_o \cos\left(\theta - (k-1)\frac{2\pi}{5} - \varphi\right), k = 1, 2, ..., 5.$$

(2)

where  $I_0$  is the output current amplitude and  $\varphi$  is the phase angle.

## 2.2 Inverter input current components

Talking about instantaneous input DC-link current i(t), it can be expressed by three components: DC (average) component  $I = I_{\rm dc}$ , low-frequency component, and high-frequency (switching frequency, few kHz) component  $\Delta i(t)$ . In the considered case of balanced load, low-frequency component is zero. Consequently, the inverter input current only contains the DC (average) and the high-frequency component, according to:

$$i(t) = I_{\rm dc} + \Delta i(t). \tag{3}$$

Under the assumption that the inverter is ideal and neglecting its losses, the input current averaged over the switching period  $T_{sw}$  can be obtained on the basis of the input/output power balance. Therefore, the averaged input current is given by (4):

$$I_{\rm dc} = \frac{5}{2} m I_0 \cos \varphi \,. \tag{4}$$

The input current i is the sum of five bridge leg currents. Each bridge leg current can be calculated from the switching function  $S_k$  = [0,1], k=1,2,...,5 (0 upper switch of the leg is OFF, 1 upper switch of the leg is ON), and corresponding output current. Consequently, the input current can be expressed as:

$$i = S_1 i_1 + S_2 i_2 + S_3 i_3 + S_4 i_4 + S_5 i_5.$$

(5)

The switching frequency input current component can be finally calculated utilising (3), (4) and (5) as:

$$\Delta i(t) = i - I_{\rm dc} = (S_1 i_1 + S_2 i_2 + S_3 i_3 + S_4 i_4 + S_5 i_5) - \frac{5}{2} m I_o \cos \varphi \,. \quad (6)$$

Due to the symmetry of the inverter input current waveforms, the analysis can be limited to one-tenth of the fundamental period (T/10), i.e. first  $\pi/5$  radians.

## 2.3 Space vector PWM equations

After application of decoupling transformation matrix onto a set of five variables (e.g. leg/phase voltages or currents), the corresponding space vectors are defined. Space vectors are usually represented by projections into two planes ( $\alpha$ - $\beta$  and x-y) and onto one axis (0-axis). This axis represents zero sequence and assuming star connection of the system it cannot be excited [5]. The  $\alpha$ - $\beta$  plane is divided into 10 sectors to find the one that it contains the reference phase voltage space vector. Then, in order to get the sinusoidal output voltages, two large and two medium neighbouring vectors are used to reach the reference in the  $\alpha$ - $\beta$  plane. The voltage references in other planes are set to zero in the linear modulation region.

By using definition of the modulation index, the reference space voltage vectors in each plane can be defined as:

$$\begin{cases} \overline{V}_1^* = \overline{V}_0^* = mVe^{j\theta} \\ \overline{V}_3^* = 0. \end{cases}$$

(7)

Since the projection of the reference phase voltage space vector forms a circle in the first plane and is zero in the second plane, the switching sequences and the application times are selected in a way to obtain these reference values on average.

The times of application (or the times applied during the modulation period to reach  $V_{\rm O}$ ) are calculated for the linear region in every  $T_{\rm sw}$ . For the first sector, the times of application of two large and two medium vectors, during one half of the switching period  $T_{\rm sw}/2$ , can be determined as:

$$t_1 = mT_{sw}K_1\sin(\pi/5 - \theta), \{10000\}$$

(8)

$$t_2 = mT_{\rm sw}K_3\sin\theta, \{11000\}$$

(9)

$$t_3 = mT_{\rm sw}K_3\sin(\pi/5 - \theta), \{11001\}$$

(10)

$$t_4 = mT_{\rm sw}K_1\sin\theta, \{11101\}$$

(11)

$$t_0 = \frac{T_{\text{sw}}}{2} - (t_1 + t_2 + t_3 + t_4)$$

$$= \frac{T_{\text{sw}}}{2} \left[ 1 - m \left( 1 + \cos \frac{\pi}{5} \right) \cos \vartheta - mK_1 \sin \vartheta \right] \{11111, 00000\}$$

(12)

being

$$K_1 = \sin\frac{\pi}{5} \approx 0.588$$

$$K_3 = \sin\frac{3\pi}{5} \approx 0.951.$$

(13)

Equations (8)–(13) can be extended to any sector s by replacing the phase angle  $\vartheta$  by  $\vartheta$ -(s-1) $\pi$ /5, s = 1, 2, ..., 10.

The application time  $t_0$  is equally shared between the two zero voltage vectors, leading to so called 'centred modulation'. The limit of the linear modulation range is  $m \le m_{\text{max}} \approx 0.526$ , where  $m_{\text{max}}$  is given according to the generalised expression given for k phases, k is odd number  $m_{\text{max}} = [2 \cos(\pi/2k)]^{-1}$ .

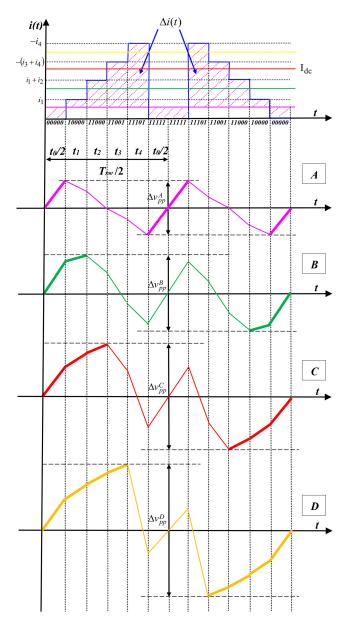

**Fig. 2** *DC-link current and voltage ripple in one*  $T_{SW}$  (a) Case A, (b) Case B, (c) Case C, (d) Case D

## 3 DC-link voltage ripple evaluation

# 3.1 Dc-link voltage components

As well as the inverter input current, the instantaneous DC-link voltage consists of three relevant components: DC (average) component V, low-frequency component, and high-frequency (switching frequency, few kHz)  $\Delta v$  component. The low-frequency DC-link voltage component is zero in considered case since it is determined on the basis of the corresponding current component. Consequently, the instantaneous DC-link voltage is expressed as:

$$v(t) = V + \Delta v(t). \tag{14}$$

In case of presence of the series DC supply resistance  $R_{\rm dc}$ , the average component V is calculated by subtracting the voltage drop on the DC supply resistance  $R_{\rm dc}$  from the DC supply voltage  $V_{\rm dc}$ , as:

$$V = V_{\rm dc} - R_{\rm dc}I_{\rm dc}. \tag{15}$$

The peak-to-peak amplitude  $\Delta v_{pp}$  of the switching frequency DC-link voltage component  $\Delta v$  can be defined as the difference between its maximum and minimum value within a switching period:

$$\Delta v_{\rm pp} = \max \left\{ \Delta v(t) \right\}_{T_{\rm sw}} - \min \left\{ \Delta v(t) \right\}_{T_{\rm sw}}. \tag{16}$$

Due to the symmetry among the five phases in the considered case of sinusoidal balanced output currents, only the first phase is examined in the following analysis.

## 3.2 Peak-to-peak voltage ripple evaluation

The peak-to-peak amplitude  $\Delta v_{\rm pp}$  of the switching frequency DC-link voltage component can be evaluated on the basis of the switching frequency current component  $\Delta i$ . Assuming that the capacitive reactance  $1/(\omega_{\rm sw}C)$  dominates the equivalent DC source impedance at the switching frequency  $(\omega_{\rm sw}=2\pi f_{\rm sw})$ , the whole  $\Delta i$  is circulating through the DC-link capacitor.

The corresponding voltage excursion can be calculated based on the equation for the voltage drop over capacitor by considering the instantaneous input current constant within each application time interval:

$$\Delta v_{\rm pp} = \frac{1}{C} \int_0^{t_{\rm pp}} |\Delta i| \mathrm{d}t \,. \tag{17}$$

The application time intervals are determined by the SV algorithm (8)–(12).

Due to the periodicity of the DC input current i(t) waveforms, the evaluation of the voltage ripple can be reduced to the phase angle range  $0 \le \theta \le \pi/5$  (the first sector of the space vector diagram). Within the first sector, depending on the value of  $I_{dc}$ , four different cases can be distinguished:

- caseA: when

$$i_1 \ge I_{dc}$$

- caseB: when  $i_1 \le I_{dc} < i_1 + i_2$

- caseC: when  $i_1 + i_2 \le I_{dc} < -(i_3 + i_4)$

- caseD: when  $-(i_3 + i_4) \le I_{dc} < -i_4$

The peak-to-peak DC-link voltage variation  $\Delta v_{pp}$  and the instantaneous input current i(t) in one switching period are depicted in Fig. 2, for all aforementioned cases.

(Case A) Evaluation in the range  $i_1 \ge I_{dc}$

According to Fig. 2 and considering application interval  $t_{pp} = t_0/2$  (bold pink trace), peak-to-peak voltage ripple can be written on the basis of (17) as

$$\Delta v_{\rm pp}^{A} = \frac{2}{C} \left( I_{\rm dc} \frac{t_0}{2} \right) = \frac{1}{C} I_{\rm dc} t_0 \,.$$

(18)

Introducing (4) and (12) into (18) leads to

$$\Delta v_{\rm pp}^A = \frac{5}{4} \frac{I_o T_{\rm sw}}{C} m \cos \varphi \left[ 1 - m \left( 1 + \cos \frac{\pi}{5} \right) \cos \vartheta - m K_1 \sin \vartheta \right]. (19)$$

(Case B) Evaluation in the range  $i_1 \le I_{dc} < i_1 + i_2$

Considering application interval  $t_{\rm pp} = t_0/2 + t_1$  (bold green trace) and conforming to Fig. 2, peak-to-peak voltage ripple can be written on the basis of (17) as

$$\Delta v_{\rm pp}^B = \frac{2}{C} \left( I_{\rm dc} \frac{t_0}{2} + (I_{\rm dc} - i_1) t_1 \right). \tag{20}$$

Considering (4), (8) and (19) leads to

$$\Delta v_{\text{pp}}^{B} = \Delta v_{\text{pp}}^{A} + \frac{2}{C} (I_{\text{dc}} - i_{1}) t_{1}$$

$$= \Delta v_{\text{pp}}^{A} + 2 \frac{I_{0} T_{\text{sw}}}{C} m K_{1} \sin\left(\frac{\pi}{5} - \vartheta\right) \left(\frac{5}{2} m \cos\varphi - \cos(\vartheta - \varphi)\right)$$

(21)

(Case C) Evaluation in the range  $i_1 + i_2 \le I_{dc} < -(i_3 + i_4)$

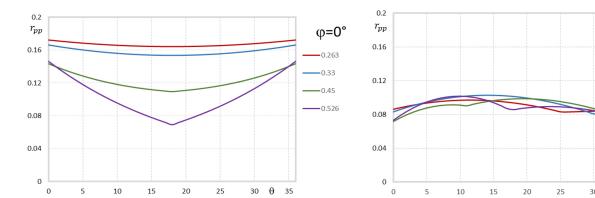

Fig. 3 Normalised peak-to-peak DC-link voltage ripple amplitude  $r_{pp}$  (9) over the period [0, 36°] for different modulation indices, m = 0.263, 0.33, 0.45 and 0.526, and output phase angles  $\varphi = 0^{\circ}$  and  $\varphi = 60^{\circ}$

**Fig. 4** Maximum of normalised peak-to-peak voltage ripple amplitude vs. modulation index for  $\varphi=0^\circ, 30^\circ, 60^\circ$  and  $90^\circ$

According to Fig. 2 and considering application interval  $t_{pp} = t_0/2 + t_1 + t_2$  (bold red trace), peak-to-peak voltage ripple can be written on the basis of (17) as

$$\Delta v_{pp}^{C} = \frac{2}{C} \left( I_{dc} \frac{t_0}{2} + (I_{dc} - i_1)t_1 + (I_{dc} - (i_1 + i_2))t_2 \right). \tag{22}$$

Taking into account (4), (9) and (21), it become (see (23))

(Case D) Evaluation in the range  $-(i_3 + i_4) \le I_{dc} < -i_4$

According to Fig. 2 and considering application interval  $t_{pp} = t_0/2 + t_1 + t_2 + t_3$  (bold orange trace), peak-to-peak voltage ripple can be written on the basis of (17) as

$$\Delta v_{\rm pp}^D = \frac{2}{C} \left( I_{\rm dc} \frac{t_0}{2} + (I_{\rm dc} - i_1)t_1 + (I_{\rm dc} - (i_1 + i_2))t_2 + (I_{\rm dc} + (i_3 + i_4))t_3 \right)$$

$$(24)$$

Considering (4), (10), and (23), peak-to-peak voltage ripple in considered range can be expressed as

$$\Delta v_{\rm pp}^{D} = \Delta v_{\rm pp}^{C} + \frac{2}{C} (I_{\rm dc} + i_3 + i_4) t_3 = \Delta v_{\rm pp}^{C} + 2 \frac{I_o T_{sw}}{C} m K_3 \sin\left(\frac{\pi}{5} - \vartheta\right) \times \left(\frac{5}{2} m \cos\varphi + \cos\left(\vartheta - \frac{4\pi}{5} - \varphi\right) + \cos\left(\vartheta - \frac{6\pi}{5} - \varphi\right)\right)$$

(25)

The actual peak-to-peak DC-link voltage ripple amplitude  $\Delta v_{pp}$  is obtained by merging the results corresponding to these four cases:

$$\Delta v_{\rm pp} = \max \left\{ \Delta v_{\rm pp}^A, \, \Delta v_{\rm pp}^B, \, \Delta v_{\rm pp}^C, \, \Delta v_{\rm pp}^D \right\}. \tag{26}$$

θ

φ=60°

0.526

Finally, from (26), one can see that the magnitude of the DC-link voltage ripple is always determined by the maximum value of those four.

DC-link peak-to-peak voltage ripple amplitude can be normalised according to

$$\Delta v_{\rm pp} = \frac{I_o T_{\rm sw}}{C} r_{\rm pp}(m, \vartheta, \varphi) \,. \tag{27}$$

Applying (27) to four cases A, B, C, and D ((19), (21), (23) and (25), respectively), the normalised peak-to-peak voltage ripple amplitude  $r_{pp}$  (m,  $\theta$ ,  $\varphi$ ) is given by

$$r_{\rm pp} = \max \left\{ r_{\rm pp}^A, r_{\rm pp}^B, r_{\rm pp}^C, r_{\rm pp}^D \right\}.$$

(28)

## 3.3 Peak-to-peak voltage ripple diagrams

In order to show the behaviour of the peak-to-peak DC voltage ripple amplitude over a fundamental period  $9 = [0, 36^{\circ}]$ , the normalised function is shown in Fig. 3 for four values of modulation index  $(0.526 = m_{\text{max}}, 0.45, 0.33, 0.263)$  and two output phase angles  $(\varphi = 0 \text{ and } \varphi = 60^{\circ})$ .

It can be noted that normalised voltage ripple amplitude  $r_{\rm pp}(9)$  has different profiles, generally ranging between 0 and 0.18. It has a higher value corresponding to the lower load phase angle, actually the highest value for the unity power factor ( $\varphi=0^{\circ}$ ), which represents the working condition for the most of grid-connected applications.

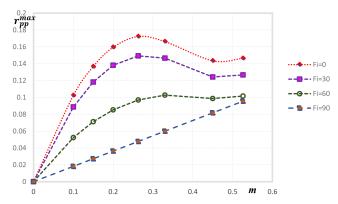

The maximum peak-to-peak voltage ripple amplitude  $r_{\rm pp}^{\rm max}(\vartheta)$  as a function of modulation index is depicted in Fig. 4 for different output phase angles. In case of  $\varphi = 90^{\circ}$ ,  $r_{\rm pp}^{\rm max}$  is determined by properly interpolating data as:

$$r_{\rm pp}^{\rm max}(\varphi = 90^{\circ}) = 0.18 \, m \,.$$

(29)

For the other values of the output phase angles ( $\varphi = 0^{\circ}$ ,  $30^{\circ}$  and  $60^{\circ}$ ), due to the cumbersome analytical determination, the maximum is not calculated analytically but the following analysis is based on Fig. 4.

# 4 DC-link capacitor design

If the switching frequency is in the order of kHz, the amplitude of the switching ripple is determined only by the size of the DC-link capacitor. Therefore, the selection and design of the DC-link

$$\Delta v_{\rm pp}^{C} = \Delta v_{\rm pp}^{B} + \frac{2}{C} (I_{\rm dc} - i_1 - i_2) t_2 = \Delta v_{\rm pp}^{B}$$

$$+ 2 \frac{I_o T_{\rm sw}}{C} m K_3 \sin \theta \left( \frac{5}{2} m \cos \varphi - \cos(\theta - \varphi) - \cos\left(\theta - \frac{2\pi}{5} - \varphi\right) \right)$$

(23)

Table 1 Simulation circuit parameters

| Tubic i         | Oirridiation circuit parameters |            |

|-----------------|---------------------------------|------------|

| Label           | Description                     | Parameters |

| v <sub>dc</sub> | DC voltage supply               | 100 V      |

| R <sub>dc</sub> | DC source resistance            | 5.5 Ω      |

| L <sub>dc</sub> | DC source inductance            | 19 mH      |

| С               | DC-link capacitance             | 1.1 mF     |

| F               | Fundamental frequency           | 50 Hz      |

| f<br>SW         | Switching frequency             | 3 kHz      |

| <sup>1</sup> 0  | Output currents amplitude       | 4.1 A      |

|                 |                                 |            |

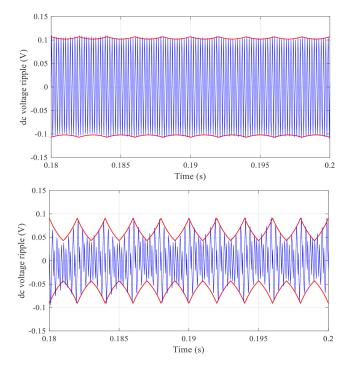

**Fig. 5** *DC-link voltage ripple (v\_{pp}): simulation results (blue trace) and calculated peak-to-peak envelope (red trace) for \varphi = 0^{\circ}, m = 0.263 (upper), m = 0.526 (lower)*

capacitor can be performed on the basis of the maximum peak-topeak voltage ripple amplitude.

Fig. 4 shows that the maximum peak-to-peak voltage ripple amplitude  $r_{\rm pp}^{\rm max}$  has the highest value for the unity power factor ( $\varphi = 0^{\circ}$ ). The following simplification can be introduced:

$$r_{\rm pp}^{\rm max} = 0.1723 \cong \frac{\sqrt{3}}{10} \to v_{\rm pp}^{\rm max} = \frac{\sqrt{3}}{10} \frac{I_o T_{\rm sw}}{C}$$

(30)

The DC-link capacitance can be easily calculated from (30) as

$$C = \frac{\sqrt{3}}{10} \frac{I_o T_{\text{sw}}}{\nu_{\text{pp}}^{\text{max}}} \tag{31}$$

In case of  $\varphi = 90^{\circ}$ ,  $r_{\rm pp}^{\rm max}$  is directly proportional to the value of modulation index m. In that case, the DC-link capacitor would be oversized if the design is based on (31). Therefore, observing Fig. 4 and considering maximum value of modulation index ( $m_{\rm max} = 0.526$ ), the following simplification can be considered:

$$r_{\rm pp}^{\rm max} = 0.095 \cong \frac{1}{10} \to v_{\rm pp}^{\rm max} = \frac{1}{10} \frac{I_o T_{\rm sw}}{C}$$

(32)

Based on (32), the DC-link capacitance can be calculated as

$$C = \frac{1}{10} \frac{I_o T_{\text{sw}}}{v_{\text{np}}^{\text{max}}} \tag{33}$$

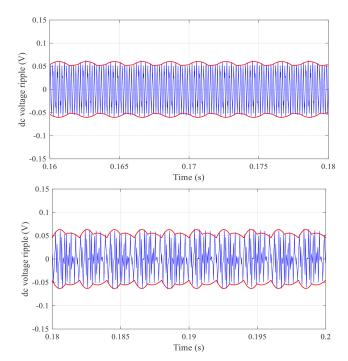

**Fig. 6** DC-link voltage ripple  $(v_{pp})$ : simulation results (blue trace) and calculated peak-to-peak envelope (red trace) for  $\varphi = 60^{\circ}$ , m = 0.263 (upper), m = 0.526 (lower)

## 5 Numerical results

The analysis of a five-phase inverter, shown in Fig. 1, was verified using Matlab/Simulink. The simulations were carried out considering the parameters given in Table 1. Continues symmetric centred PWM technique is used for VSI control.

The DC-link voltage switching ripple obtained by simulation (blue trace) is shown in Figs. 5 and 6. In the same figures, the corresponding envelopes, calculated based on Section 3, are shown as well (red traces). The envelopes are calculated as one half of the peak-to-peak voltage ripple value. Two cases of the output phase angles  $\varphi = 0^{\circ}$  (Fig. 5) and  $\varphi = 60^{\circ}$  (Fig. 6) are considered for  $m_{\text{max}}$  and  $m_{\text{max}}/2$ .

Obtained simulation results show good matching with calculated envelopes, for all considered cases in the whole fundamental period.

# 6 Conclusion

Here, in order to properly design and select the DC-link capacitor, the detailed analysis of the DC-link voltage ripple in five-phase PWM voltage source inverters with balanced load has been carried out.

The amplitude of the DC-link voltage switching ripple is analytically derived as a function of modulation index, and the amplitude of output current and phase angle. Different diagrams are introduced in order to show peak-to-peak voltage ripple distribution as well as its maximum amplitude as a function of modulation index. Based on the maximum peak-to-peak DC-link voltage ripple amplitude, simple and practical equations for designing the DC-link capacitor are proposed.

In order to verify proposed developments, simulations have been carried out by Matlab/Simulnik considering full range of modulation index and output phase angle. The obtained results show a very good agreement.

#### 7 References

- [1] Levi, E.: 'Multiphase electric machines for variable speed applications', *IEEE Trans. Ind. Electr.*, 2008, 55, pp. 1893–1908

- Parsa, L.: 'On advantages of multi-phase machines'. Proc. of IEEE IECON, Raleigh, NC, 2005, pp. 1574–1579

- [3] Levi, E.: 'Advances in converter control and innovative exploitation of additional degrees of freedom for multiphase machines', *IEEE Trans. Ind. Electron.*, 2016, 63, pp. 433–448

- [4] Grandi, G., Serra, G., Tani, A.: 'General analysis of multi-phase systems based on space vector approach'. Proc. of EPE-PEMC, Portoroz, Slovenia, 2006, CD-ROM paper T2409

[5] Iqbal, A., Levi, E.: 'Space vector modulation schemes for a fivephase voltage

- [5] Iqbal, A., Levi, E.: 'Space vector modulation schemes for a fivephase voltage source inverter'. Proc. of EPE, Dresden, Germany, 2005, CD-ROM paper, pp. P1–12

- [6] Oleschuk, V., Profumo, F., Tenconi, A., et al.: 'Five-phase inverters with synchronized PWM'. Proc. of IEEE EUROCON, Warsaw, Poland, 2007, pp. 1872–1878

- [7] Graditi, G., Griva, G., Oleschuk, V.: 'Overmodulation control of five phase inverters with full DC-bus voltage utilization'. Proc. of IEEE SPEEDAM Symp., Pisa, Italy, 2010, pp. 1150–1155

- [8] Lega, M., Mengoni, G., Tani, S.A., et al.: 'General theory of space vector modulation for five-phase inverters'. Proc. of IEEE Int. Symp. on Industrial Electronics, Cambridge, U.K., 2008, pp. 237–244

- Electronics, Cambridge, U.K., 2008, pp. 237–244

deSilva, P.S.N., Fletcher, J.E., Williams, B.W.: 'Development of space vector modulation strategies for five-phase voltage source inverters'. Proc. of IEE Power Electronics, Machines and Drives, Edinburgh, U.K., 2004, pp. 650–655

- [10] Muqorobin, P., Dahono, A., Purwadi, A.: 'Optimum phase number for multiphase PWM inverters'. Proc. of Conf. on Electrical Engineering, Computer Science and Informatics, Yogyakarta, Indonesia, 2017, pp. 1–6

- [11] Kolar, J.W., Round, S.D.: 'Analytical calculation of the RMS current stress on the DC-link capacitor of voltage-PMW converter system', *IEE Proc. Electr. Power Appl.*, 2006, 153, (4), pp. 535–543

- [12] Dahono, P.A., Sato, Y., Kataoka, T.: 'Analysis and minimization of ripple components of input current and voltage of PWM inverters', *IEEE Trans. Ind. Appl.*, 1996, 32, pp. 945–950

- [13] Bierhoff, M.H., Fuchs, F.W.: 'DC-link harmonics of three-phase voltage-source converters influenced by the pulsewidth-modulation strategy-an analysis', *IEEE Trans. Ind. Electr.*, 2008, 55, pp. 2085–2092

3714

- [14] Deng, H., Helle, L., Bo, Y., et al.: 'A general solution for theoretical harmonic components of carrier based PWM schemes'. Proc. of IEEE Applied Power Electronics Conf. and Exposition. Washington. DC. 2009. pp. 1698–1703

- Electronics Conf. and Exposition, Washington, DC, 2009, pp. 1698–1703

Lu, X., Peng, F.Z.: 'Minimizing DC capacitor current ripple and DC capacitance requirement of the HEV converter/inverter systems'. Proc. of IEEE Energy Conversion Congress and Exposition, San Jose, CA, 2009, pp. 1191–1198

- [16] Grandi, G., Loncarski, J.: 'Evaluation of current ripple amplitude in fivephase PWM voltage source inverters'. Proc. of IEEE EUROCON, Zagreb, Croatia, 2013, pp. 1073–1080

- [17] Loncarski, J., Dordevic, O., Grandi, G.: 'Experimental verification of current ripple amplitude in five-phase PWM VSIs'. Proc. of IEEE IECON, Vienna, Austria, 2013, pp. 5183–5188

- [18] Jiang, D., Wang, F.: 'A general current ripple prediction method for the multiphase voltage source converter', *IEEE Trans. Power Electr.*, 2014, 29, pp. 2643–2648

- [19] Dahono, P.A., Deni, ., Akbarifutra, C.P., et al.: 'Input ripple analysis of five-phase pulse width modulated inverters', *IET Power Electr.*, 2010, **3**, pp. 716–723

- [20] Vujacic, M., Srndovic, M., Hammami, M., et al.: 'Evaluation of DC voltage ripple in single-phase H-bridge PWM inverters'. Proc. IEEE IECON, Florence, Italy, 2016, pp. 3235–3240

- [21] Vujacic, M., Hammami, M., Srndovic, M., et al.: 'Theoretical and experimental investigation of switching ripple in the DC-link voltage of single-phase H-bridge PWM inverters', Energies, 2017, 10, pp. 1–6

- [22] Vujacic, M., Hammami, M., Srndovic, M., et al.: 'Evaluation of DC voltage ripple in three-phase PWM voltage source inverters'. Proc. IEEE Int. Symp. on Industrial Electronics, Edinburgh, U.K, 2017, pp. 711–716