Received 29 November 2017; revised 8 January 2018; accepted 10 January 2018. Date of publication 12 January 2018; date of current version 26 January 2018.

The review of this paper was arranged by Editor C. C. McAndrew.

Digital Object Identifier 10.1109/JEDS.2018.2792539

# Hot-Carrier Degradation in Power LDMOS: Selective LOCOS- Versus STI-Based Architecture

ANDREA NATALE TALLARICO<sup>®</sup> <sup>1</sup>, SUSANNA REGGIANI<sup>®</sup> <sup>1</sup>, RICCARDO DEPETRO<sup>2</sup> (Member, IEEE), ANDREA MARIO TORTI<sup>2</sup>, GIUSEPPE CROCE<sup>2</sup> (Member, IEEE), ENRICO SANGIORGI<sup>1</sup> (Fellow, IEEE), AND CLAUDIO FIEGNA<sup>1</sup>

1 Advanced Research Center on Electronic System, Department of Electrical, Electronic, and Information Engineering, University of Bologna, 47521 Cesena, Italy 2 Technology Research and Development, STMicroelectronics, 20864 Agrate Brianza, Italy

CORRESPONDING AUTHOR: A. N. TALLARICO (e-mail: a.tallarico@unibo.it)

This work was supported by the R2POWER300 "Preparing R2 Extension to 300 mm for BCD Smart Power and Power Discrete" under Grant ECSEL 2014-2-653933.

ABSTRACT In this paper, we present an analysis of the degradation induced by hot-carrier stress in new generation power lateral double-diffused MOS (LDMOS) transistors. Two architectures with the same nominal voltage and comparable performance featuring a selective LOCOS and a shallow-trench isolation are investigated by means of constant voltage stress measurements and TCAD simulations. In particular, the on-resistance degradation in linear regime is experimentally extracted and numerically reproduced under different stress conditions. A similar amount of degradation has been reached by the two architectures, although different physical mechanisms contribute to the creation of the interface states. By using a recently developed physics-based degradation model, it has been possible to distinguish the damage due to collisions of single high-energetic electrons (single-particle events) and the contribution of colder electrons impinging on the silicon/oxide interface (multiple-particle events). A clear dominance of the single-electron collisions has been found in the case of LOCOS structure, whereas the multiple-particle effect plays a clear role in STI-based device at larger gate-voltage stress.

**INDEX TERMS** Hot-carrier degradation/stress, on-resistance degradation, LOCOS, STI, single-particle process, multiple-particle process, TCAD simulation.

#### I. INTRODUCTION

Lateral double-diffused MOS (LDMOS) power transistor is broadly used for relatively high voltage applications and smart power technologies due to its low on-resistance (R<sub>ON</sub>) [1], [2] and to its compatibility with standard CMOS process [3], [4].

As the technology scales down, the development of the devices in the new technology platforms becomes more challenging in terms of optimization of performance and reliability [5]. Usually, the shallow-trench isolation (STI) is adopted in the drift region as field insulator to further increase the voltage rate with limited device area [6]. R<sub>ON</sub> can be further reduced by optimizing the doping concentration. However, it is well known that current crowing at the STI corner leads to significant hot-carrier degradation, worsening the device reliability [7]. In particular, when the device operates in ON-state regime, electrons can gain sufficient kinetic energy (hot-carriers) necessary to create interface

states followed by charge trapping causing the reduction of the device performance [8]. For this reason, the LOCOS process has been recently re-engineered for power devices in order to obtain customized shapes [9].

Although the first observation of hot-carrier degradation phenomenon in LDMOS transistors dates back to over twenty years ago [10], the underlying different physical mechanisms and their playing role in device degradation are not completely clear yet. As a result, there is still a strong interest in understanding and controlling the hot-carrier related degradation in power LDMOS transistors, especially for the Semiconductor Industries.

Recently, many studies have been proposed in [11]–[18]. Li *et al.* [11] have shown that by optimizing the drift region layout, more specifically, by reducing the overlap between N-drift region and poly-gate and by extending the overlap implantation between N-drift and P-well, the hot-carrier degradation is attenuated since the lateral electric field is

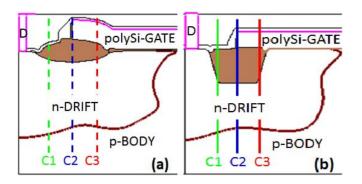

FIGURE 1. Sketch of the N-drift region in the case of (a) selective LOCOSand (b) STI-based LDMOS transistors (not in scale). Cuts C1, C2, and C3 represent the sections where interface (oxide/N-drift) trapped charge is monitored.

reduced and the impact ionization is moved away from the Si/SiO<sub>2</sub> interface.

In [13], a novel device structure with a poly-gate partly recessed into the field oxide has been presented to optimize the on-resistance degradation at the worst HCS condition, whereas the impact of the STI angle on hot-carrier stress has been investigated in [15].

Sharma *et al.* [17], by studying the hot-carrier degradation in n- and p-channel LDMOS transistors found out that the role of the colder (multiple) carriers must be taken into account in order to numerically and accurately reproduce the on-resistance degradation for both short and long stress times.

Finally in [18], by performing long-term HC stress at different biases and temperatures, we have demonstrated that in the case of a customized thick oxide architecture (selective LOCOS), the dominant role inducing hot-carrier degradation is played by the single highly energetic electrons.

In this paper, a comparison study of the degradation induced by hot-carrier stress in selective LOCOS- and STI-based n-channel LDMOS transistors is reported, aiming at understanding the different underlying mechanisms and how their roles depend on the type of device architecture. By combining experimental and simulation analyses, it has been demonstrated that similar degradation shifts can be achieved in architectures with similar performances, although different physical mechanisms contribute to the interface-trap generation.

## II. DEVICES STRUCTURE AND TCAD CALIBRATION

N-channel selective LOCOS- and STI-based power LDMOS transistors, fabricated on 200mm silicon wafers by STMicroelectronics, are considered and sketched in Fig. 1a and 1b, respectively. Doping profiles and key geometrical dimensions have been properly designed to secure same medium voltage capability with the two different field oxide architectures. A sketch of the drift region is shown in Fig. 1, representing the region where, as detailed in the following, the major contribution to degradation during hot-carrier stress is localized.

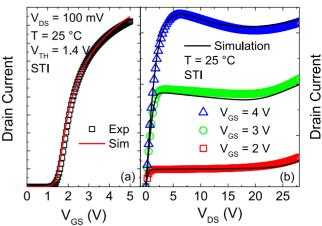

FIGURE 2. Experimental (symbols) and simulated (line) (a) transferand (b) output-characteristics of the STI-based architecture reported in Fig. 1b. Similar curves for LOCOS have been reported in [18].

In order to investigate the device degradation due to hotcarrier stress (HCS) and to understand which are the dominant underlying physical mechanisms, experimental analyses have been performed combined with TCAD simulations.

The device degradation has been experimentally carried out on-wafer by means of constant voltage stress (CVS) measurements. Consequently, HCS induced degradation is extracted by monitoring the R<sub>ON</sub> shift in linear regime.

Finally, the simulated structures have been defined and calibrated in the frame of the Sentaurus TCAD simulator [19] considering the geometric characteristics and the material properties of the devices under test (DUT). In particular, the transport problem has been solved by using the electrothermal model, which couples the drift-diffusion transport with the heat flow equation. Special consideration has been given to the choice of the simulation set-up. The impurity concentration within the cross section has been inferred from process simulation results. All measured devices have widths that are significantly large so to prevent undesired non-uniformity along the width of the device.

A tuning of the deck was carried out through the comparison with measured turn-on and output curves. More specifically, acceptor traps have been added at the Si/SiO<sub>2</sub> interface of the channel region in order to accurately predict the measured threshold voltage and trans-conductance, as shown in Fig. 2a for the STI-based device.

In order to reproduce the self-heating effects, proper thermal boundary conditions have been applied in the numerical set-up calibrated against the measured output curves. In addition, the UniBo impact-ionization model available in the Synopsys tool has been selected due to its extended field and temperature validity range [19], [20]. It has been slightly tuned to find an accurate prediction of the avalanche onset at larger V<sub>DS</sub> in the STI-based device (Fig. 2b).

The same procedure has been adopted also for the case of the selective LOCOS device as reported in detail in [18].

### III. HOT-CARRIER STRESS DEGRADATION MODEL

In order to model hot-carrier stress, the numerical solution of the full-band Boltzmann Transport Equation (BTE) implemented in [19] has been used to predict the energetic distribution of hot electrons. The physics-based model recently developed in [21] has been adopted in the numerical analysis as it has been demonstrated to be specifically suited for the TCAD analysis of the parameter drifts under electrical stress of LDMOS devices.

Different competing mechanisms such as single-particle (SP), multiple-particle (MP) and field-enhanced thermal interaction (TH) may contribute to the de-passivation of the electrically inactive bonds at the silicon/oxide interface.

SP process is related to a single high energetic particle which can induce a bond-breakage event in a single collision [17], [21], whereas MP-process is triggered by a series of colder carriers which subsequently impinge the interface causing the bond breaking [21], [22]. Finally, the TH-process is related to thermal interactions with the lattice. In particular, due to high lattice temperature, phonons can excite the silicon interface molecules and eventually break their bonds [21], [23].

The degradation model gives as output the interface-trap density  $N_{it}(t)$  mapped at each (x, y) position along the Si/SiO<sub>2</sub> interface of the device, allowing to directly simulate the turn-on curve in stressed conditions at any stress time. The generated  $N_{it}$  distribution has been incorporated in the simulation set-up by assuming an acceptor trap density with a single energy level at mid-gap, leading to fully occupied interface states. The degradation model parameters have been calibrated against experiments and validated over an extended range of biases and temperatures on both devices as illustrated in the following.

# IV. RESULTS AND DISCUSSION

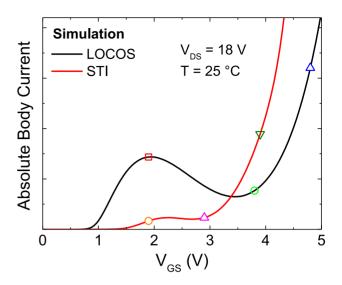

Fig. 3 shows the simulated body current for both selective LOCOS- and STI-based LDMOS transistors. It is worth noting that it was not possible to experimentally monitor the body current because body and source contacts are internally short-circuited in the real devices.

In both devices, an initial body current rise is shown. It is attributed to the steep increase of the channel current in the near-threshold regime, with carriers experiencing a region of high electric field close to the channel. Subsequently, by further increasing the gate bias the impact ionization peak moves toward the drain (shown in [18]) and the body current rises again to larger values due to the Kirk effect at the drain edge.

By comparing the two architectures, it is possible to note that the STI-device features a lower body current peak at relatively low gate voltages, hence a lower impact-ionization generation. Vice versa, when the electric field peak is moved to the drain region at high  $V_{GS}$ , the STI-LDMOS shows a larger body current increase, indicating a larger local electric field in the structure. The different body current values

FIGURE 3. Simulated body current in the case of selective LOCOS- and STI-based LDMOS transistors. Higher impact ionization generation (body current peak) is shown in the case of LOCOS architecture. No y-axis is displayed for confidentiality reasons.

are the global result of the different field plate architectures leading to different doping profiles and geometrical dimensions for device optimization.

By considering the trend of the simulated body currents in Fig. 3, three different stress conditions for each architecture have been chosen to verify a possible correlation between impact ionization (hot-carrier) and device HCS degradation.

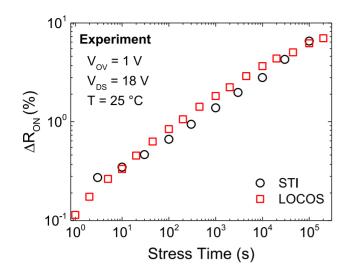

The experimental (symbols) and simulated (lines) onresistance degradation curves extracted in linear regime for the three selected stress conditions in the case of selective LOCOS- and STI-based devices is reported in Figs. 4a and 4b, respectively.

First, by focusing on the experimental data (symbols) it is possible to notice that a clear correlation between simulated body current (Fig. 3) and  $R_{ON}$  degradation is only shown in the case of LOCOS devices (Fig. 4a). More specifically, the higher the body current (absolute value), the larger the extracted  $\Delta R_{ON}$ . Differently, the STI-LDMOS shows significant changes in the degradation curves even if the body current values are similar (see the curves at  $V_{GS}=1.9~V$  and 2.9~V in Fig. 4b). Moreover, at larger gate biases ( $V_{GS}=3.9~V$ ) the significant higher body current does not result in a higher  $\Delta R_{ON}$  as for the LOCOS case ( $V_{GS}=4.8~V$ ). These differences suggest that the onresistance degradation in the two architectures is triggered by different underlying physical mechanisms.

In general, a clear link between body current, hence impact ionization generation, and  $R_{\rm ON}$  degradation suggests that the single high energetic carrier (hot-carrier) is the dominant source causing a bond-breaking event in a single collision, leading to interface-traps generation. For this reason, only the single-particle process was incorporated in the HCS degradation model in order to simulate the  $R_{\rm ON}$  degradation in the LOCOS devices [18]. The accurate agreement

VOLUME 6, 2018 221

FIGURE 4. Experimental and simulated  $R_{ON}$  degradation in (a) selective LOCOS- and (b) STI-based LDMOS. While a direct correlation between body current (Fig. 3) and  $\Delta R_{ON}$  is shown in LOCOS devices (a), same behavior is not reported for STI devices (b).

of the numerical predictions with experiments shown in Fig. 4a confirms that the single-electron HCS process is the most relevant one for this kind of architecture.

Differently, by adopting the same approach in the case of STI-based LDMOS, i.e., simulating the  $R_{ON}$  degradation by simply accounting for the SP process, a significant underestimation of the degradation curves has been obtained as shown by the dashed lines in Fig. 4b, except for  $V_{GS}=1.9\ V$  where the single particle process turns out to be the dominant degradation mechanism.

Therefore, in addition to the SP contribution, the multiple-particle process has been incorporated in the TCAD degradation simulation and the experimental  $R_{ON}$  degradation curves have been accurately reproduced also in the case of the STI device (solid lines in Fig. 4b), confirming that different physical degradation mechanisms occur in the two architectures.

It is worth noting that the corresponding models (singleand multiple-particle contributions) have been initially calibrated against the  $R_{ON}$  degradation experiments, mainly by changing the fitting parameters which modulate the reaction cross-section and the probabilities of defect

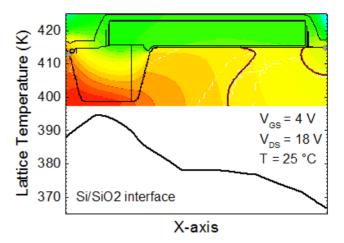

FIGURE 5. Lattice temperature, due to self-heating effect, along the silicon/oxide interface in the case of STI architecture at high gate voltage. It is worth noting that LOCOS device feature a lower temperature (not shown).

generation [18], [21], in order to tune the magnitude and slope of the drift curves. Slightly different parameters have been adopted for the two architectures. In particular, the different probabilities for defects generation are due to the simultaneous presence of two competing mechanisms in STI (SP and MP) rather than only one in LOCOS (SP), whereas the different constant in the reaction cross-section should be ascribed to the different oxide interface in the two structures. More specifically, the silicon is chemically etched and differently crystal-oriented (side walls) in STI devices.

The thermal contribution (TH process) to HCS degradation has not been accounted for in the simulation since it is strongly dependent on the lattice temperature and thus becomes crucial in high power devices where the current rating induces relevant self-heating effects. By observing Fig. 5, a relatively low lattice temperature along the Si/SiO<sub>2</sub> interface of the STI device is shown. In particular, a temperature lower than 125 °C is shown although a high gate voltage is applied (close to the maximum nominal value), confirming that TH-related trap generation is negligible for this device class voltage.

It is worth noting that the maximum temperature in the case of LOCOS devices at the same drain and overdrive voltage is even lower than the STI-based LDMOS one (not shown).

No relevant threshold voltage shift (within 1% at  $10^5$  s of stress) has been experimentally observed for the examined gate-voltage window in long-term stressed devices in both structures (not shown). Therefore, no significant degradation is expected in the channel region and hence the field-enhanced thermal contribution at large gate biases, usually found in high power/voltage LDMOS transistors, is negligible. This is also consistent with the limited increase of temperature induced by self-heating in the channel region (Fig. 5).

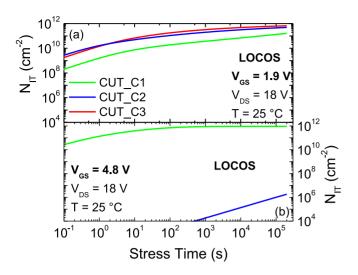

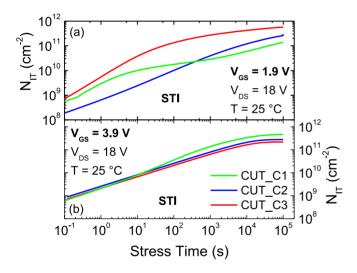

FIGURE 6. Interface trap concentration versus the stress time in correspondence to the cuts shown in Fig. 1 (C1 is the closest cut to the drain side) for the stress conditions (a)  $V_{GS}=1.9$  V and (b)  $V_{GS}=4.8$  V at  $V_{DS}=18$  V and T=25 °C. It is worth noting that cut C3 is not shown in (b) because the  $N_{IT}$  generation is below  $10^4$  cm $^{-2}$ , hence negligible.

FIGURE 7. Interface trap concentration versus the stress time in correspondence of the cuts shown in Fig. 1 (C1 is the closest cut to the drain side) for the stress conditions (a)  $V_{GS}=1.9\ V$  and (b)  $V_{GS}=3.9\ V$  at  $V_{DS}=18\ V$  and  $T=25\ ^{\circ}C$ . Similar results have been shown in [18] for LOCOS devices.

As shown in the case of LOCOS devices in [18], the simulated interface trap creation can be monitored during the stress at different positions along the Si/SiO<sub>2</sub> interface. Similar cut positions have been monitored also in the STI device as indicated in Fig. 1, allowing for a direct comparison of the critical hot spots in both devices at different stress biases. In Figs. 6 and 7, the interface-trap concentrations as a function of time are reported for the LOCOS and STI structures, respectively.

By observing Fig. 7, it is possible to note that at relatively low gate voltages (a) the highest and dominant interface trap creation occurs close to the source-side corner of the STI (C3 of Fig. 1), whereas at relatively high  $V_{GS}$  (b) the

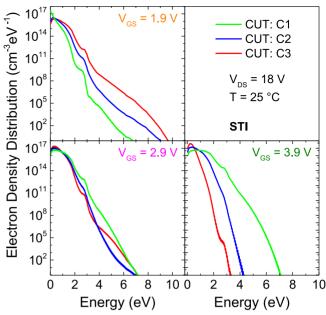

FIGURE 8. Electron density distribution as a function of different gate voltages, evaluated at the Si/SiO<sub>2</sub> interface of the STI in correspondence of the cutline shown in Fig. 1.

trap generation is spread on the whole STI bottom part, and becomes slightly pronounced at the drain edge (C1) for longer stress times.

This is consistent with the physical mechanisms behind the interface trap generation. In particular, at low gate voltages the single-particle is the dominant process causing  $R_{ON}$  degradation in both devices. At such bias condition electrons experience a region of high electric field close to the channel, hence close to the STI corner or to the LOCOS bird's beak on the source side, gaining high kinetic energy and favoring interface-trap creation in that region.

By increasing the gate bias, in both structures the longitudinal electric field peak is redistributed and moves toward the drain contact alleviating the hot-carriers contribution. On the other hand, the higher drain current density provides many colder carriers at the STI interface able to interact with molecules and break bonds. The STI depth induces a large current density at the Si/SiO<sub>2</sub> interface, leading to a significant trap formation along the whole path (Fig. 7b), which was not visible in the LOCOS case.

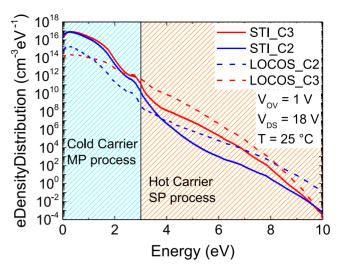

Fig. 8 strengthens the latter statements showing the electron energy distribution as a function of different gate biases at the Si/SiO<sub>2</sub> interface in correspondence of the cut lines shown in Fig. 7. In particular, it is possible to note that by increasing the gate voltage the electron density remains high in all three positions along the STI, while energy distribution shows a clear reduction of the hot electrons, suggesting a dominant presence of colder carriers and the reduction of hot electrons.

In the case of selective LOCOS, the electron density at the interface tends to decrease by increasing the gate voltage,

VOLUME 6, 2018 223

FIGURE 9. Experimental on-resistance degradation in the case of selective LOCOS- and STI-based LDMOS transistors at the same overdrive and drain voltage.

thus no cold particles are available to damage the oxide. Since the single high energetic electron is the dominant degradation mechanism independently of the gate bias, the region interested to interface trap creation is linked to the position of the impact ionization peak, i.e., the region where electrons experience the highest kinetic energy. In particular, by increasing the gate voltage the interface trap generation clearly moves from source-side to drain-side of the LOCOS region [18].

Finally, in order to further and directly compare selective LOCOS- and STI-based architectures, hot-carrier stresses at the same overdrive voltage have been performed and shown in Fig. 9. A similar amount of R<sub>ON</sub> degradation is reported for both architectures although different underlying physical mechanisms occur. As an overdrive of 1 V has been considered, the most significant contribution to degradation is expected to be localized at the source-side corner and in the middle of the isolation region (C2 and C3 positions). By comparing the body currents in Fig. 3, a much lower amount of hot electrons is expected in the STI case. In Fig. 10, the electron energy distribution at the Si/SiO2 interface is shown in both architectures for the stress condition considered in Fig. 9. It is clearly found that the STI device features a higher density of colder carriers (< 3 eV), whereas the LOCOS architecture shows a higher density of hot-carriers (> 3 eV).

On the overall, the selective LOCOS architecture is significantly sensitive to hot-carrier induced degradation (single-particle), whereas in the STI device the lower single high energetic electron contribution is compensated by the colder carriers (multiple-particle), resulting in a similar  $R_{\rm ON}$  degradation.

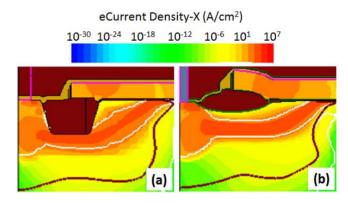

The role played by the insulator depth is clearly visible in Fig. 11, showing the current density in the two devices at the same gate overdrive. In the case of the LOCOS

FIGURE 10. Electron density distribution evaluated at the Si/SiO<sub>2</sub> interface (cuts C2 and C3) of the STI and LOCOS devices at the stress condition considered in Fig. 9.

FIGURE 11. Longitudinal electrons current density in the case of (a) STI- and (b) selective LOCOS-based LDMOS transistors at  $V_{OV}=1$  V,  $V_{DS}=18$  V and T=25 °C. Since STI region is deeper than LOCOS one, electrons current is confined at the STI bottom.

structure, the source-to-drain current flows far away from Si/SiO<sub>2</sub> interface, thus a low number of colder electrons is present at the interface. In the case of the STI device, being the etched trench deeper in silicon, the current flows confined/compressed at the interface of the STI bottom. As a result, a higher number of electrons interact with the molecules at the interface. A similar result was found in [12], showing the simulated HCS drift curves of STI-based LDMOS devices with different oxide thicknesses: in a thinner STI case, the concurrent effects of a lower surface current density and a higher carrier temperature are observed with respect to the thicker one, leading to limited HCS drift variations.

### V. CONCLUSION

In this paper, we investigated the degradation induced by hot-carrier stress in new generation power LDMOS transistors, exploiting two different architectures such as selective LOCOS and Shallow-Trench Isolation.

In particular, the on-resistance degradation in linear regime has been experimentally evaluated under different stress conditions and numerically reproduced to understand the different underlying physical mechanisms affecting the device reliability during ON-state operation.

As the device technology is very similar, the performance and reliability can be directly compared to understand the role played by the different insulating structures on the hot-carrier stress degradation. The main results of this investigation is the determination of the role played by single-particle and multiple-particle processes in the two cases.

The STI devices clearly show a significant improvement in terms of reduced impact-ionization contribution to the body current due to the global result of different doping profiles and geometrical dimensions, which leads to a clear reduction of the single-particle events during long-term hot-carrier degradation. However, due to the depth of the STI trench, a high current density is experienced at the STI bottom promoting trap generation due to multiple-particle processes, which eventually leads to comparable hot-carrier stress degradation.

#### **REFERENCES**

- [1] K. Shirai, K. Yonemura, K. Watanabe, and K. Kimura, "Ultra-low onresistance LDMOS implementation in 0.13μm CD and BiCD process technologies for analog power IC's," in *Proc. IEEE ISPSD*, Barcelona, Spain, Jun. 2009, pp. 77–79, doi: 10.1109/ISPSD.2009.5158005.

- [2] W. Ge et al., "Ultra-low on-resistance LDMOS with multi-plane electron accumulation layers," *IEEE Electron Device Lett.*, vol. 38, no. 7, pp. 910–913, Jul. 2017, doi: 10.1109/LED.2017.2701354.

- [3] M. Li, J.-M. Koo, and R. V. Purakh, "0.18μm BCD technology platform with performance and cost optimized fully isolated LDMOS," in *Proc. IEEE EDSSC*, Singapore, Jun. 2015, pp. 820–822, doi: 10.1109/EDSSC.2015.7285244.

- [4] T.-H. Lee and P. A. Abshire, "Design and characterization of high-voltage NMOS structures in a 0.5 μm standard CMOS process," *IEEE Sensors J.*, vol. 13, no. 8, pp. 2906–2913, Aug. 2013, doi: 10.1109/JSEN.2013.2263795.

- [5] P. Moens et al., "A comprehensive model for hot carrier degradation in LDMOS transistors," in Proc. IEEE IRPS, Phoenix, AZ, USA, Apr. 2007, pp. 492–497, doi: 10.1109/RELPHY.2007.369940.

- [6] S. Haynie et al., "Power LDMOS with novel STI profile for improved RsP, BVdss, and reliability," in Proc. IEEE ISPSD, Hiroshima, Japan, Jun. 2010, pp. 241–244.

- [7] J. F. Chen, K.-S. Tian, S.-Y. Chen, K.-M. Wu, and C. M. Liu, "On-resistance degradation induced by hot-carrier injection in LDMOS transistors with STI in the drift region," *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 1071–1073, Sep. 2008, doi: 10.1109/LED.2008.2001969.

- [8] J. F. Chen, K.-S. Tian, S.-Y. Chen, K.-M. Wu, and C. M. Liu, "On-resistance degradation induced by hot-carrier injection in LDMOS transistors with STI in the drift region," *IEEE Electron Device Lett.*, vol. 29, no. 9, pp. 1071–1073, Sep. 2008, doi: 10.1109/LED.2008.2001969.

- [9] R. Roggero et al., "BCD8sP: An advanced 0.16 μm technology platform with state of the art power devices," in Proc. IEEE ISPSD, Kanazawa, Japan, May 2013, pp. 361–364, doi: 10.1109/ISPSD.2013.6694422.

- [10] R. Versari, A. Pieracci, S. Manzini, C. Contiero, and B. Riccio, "Hot-carrier reliability in submicrometer LDMOS transistors," in *Proc. IEEE IEDM*, Washington, DC, USA, Dec. 1997, pp. 371–374, doi: 10.1109/IEDM.1997.650402.

- [11] R. Li et al., "A study of 28nm LDMOS HCI improvement by layout optimization," in Proc. IEEE CSTIC, Shanghai, China, May 2017, pp. 1–4, doi: 10.1109/CSTIC.2017.7919741.

- [12] S. Reggiani et al., "Analysis of HCS in STI-based LDMOS transistors," in Proc. IEEE IRPS, Anaheim, CA, USA, May 2010, pp. 881–886, doi: 10.1109/IRPS.2010.5488712.

- [13] S. Liu et al., "Hot-carrier-induced degradations and optimizations for lateral DMOS transistor with multiple floating poly-gate field plates," *IEEE Trans. Electron Devices*, vol. 64, no. 8, pp. 3275–3281, Aug. 2017, doi: 10.1109/TED.2017.2711276.

- [14] S. Poli et al., "Investigation on the temperature dependence of the HCI effects in the rugged STI-based LDMOS transistor," in Proc. IEEE ISPSD, Hiroshima, Japan, Jun. 2010, pp. 311–314.

- [15] A. F. M. Alimin, H. H. Hizamul-Din, S. F. W. M. Hatta, and N. Soin, "The influence of shallow trench isolation angle on hot carrier effect of STI-based LDMOS transistors," in *Proc. IEEE RSM*, Batu Ferringhi, Malaysia, Aug. 2017, pp. 248–251, doi: 10.1109/RSM.2017.8069149.

- [16] S. Poli et al., "Full understanding of hot-carrier-induced degradation in STI-based LDMOS transistors in the impact-ionization operating regime," in *Proc. IEEE ISPSD*, San Diego, CA, USA, May 2011, pp. 152–155, doi: 10.1109/ISPSD.2011.5890813.

- [17] P. Sharma et al., "Modeling of hot-carrier degradation in LDMOS devices using a drift-diffusion based approach," in Proc. IEEE SISPAD, Washington, DC, USA, Sep. 2015, pp. 60–63, doi: 10.1109/SISPAD.2015.7292258.

- [18] A. N. Tallarico et al., "Investigation of the hot carrier degradation in power LDMOS transistors with customized thick oxide," Microelectronics Rel., vols. 76–77, pp. 475–479, Sep. 2017, doi: 10.1016/j.microrel.2017.07.043.

- [19] Sentaurus-Device U.G. v. L-2016.03, Synopsys Inc., Mountain View, CA, USA, 2016.

- [20] S. Reggiani et al., "Measurement and modeling of the electron impactionization coefficient in silicon up to very high temperatures," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2290–2299, Oct. 2005, doi: 10.1109/TED.2005.856807.

- [21] S. Reggiani et al., "TCAD simulation of hot-carrier and thermal degradation in STI-LDMOS transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 2, pp. 691–698, Feb. 2013, doi: 10.1109/TED.2012.2227321.

- [22] P. Sharma et al., "The role of cold carriers and the multiple-carrier process of Si-H bond dissociation for hot-carrier degradation in n- and p-channel LDMOS devices," Solid-State Electron., vol. 115, pp. 185–191, Jan. 2016, doi: 10.1016/j.sse.2015.08.014.

- [23] S. Reggiani et al., "Characterization and modeling of electrical stress degradation in STI-based integrated power devices," Solid-State Electron., vol. 102, pp. 25–41, Dec. 2014, doi: 10.1016/j.sse.2014.06.008.

ANDREA NATALE TALLARICO received the Ph.D. degree in electronic engineering from the University of Bologna, Italy, 2017. In 2013, he joined the Advanced Research Center for Electronic Systems, Cesena, Italy, where he is currently a Post-Doctoral Researcher, involved in the characterization and modeling of semiconductor power devices reliability. From 2012 to 2016, he was a visiting student with the IMEC vzw Research Center, Leuven, Belgium.

**SUSANNA REGGIANI** received the Ph.D. degree in electrical engineering from the University of Bologna, Italy, in 2001, where she is an Associate Professor with the Faculty of Engineering and has been with the Department of Electronics and the Advanced Research Center for Electronic Systems, since 2001. Her scientific activity has been devoted to the physics, modeling and characterization of electron devices, with special emphasis on transport models in semiconductors.

**RICCARDO DEPETRO** (M'97) received the Electronic Engineering Laurea degree from the Politecnico di Milano, in 1990. He is a Senior Member of Technical Staff with STMicroelectronics and researches on new power devices architecture and integration.

VOLUME 6, 2018 225

ANDREA MARIO TORTI received the Ph.D. degree in physics from the Politecnico of Milan, Italy, in 2013. In the same year, he joined STMicroelectronics, where he is a Senior Technology Development Engineer with the Smart Power Technology Research and Development Team. He is currently researching the development of advanced bipolar CMOS DMOS technology high voltage power devices.

**ENRICO SANGIORGI** (F'05) received the Laurea degree from the University of Bologna, in 1979. He has been a Visiting Scientist with Stanford University, Stanford, CA, USA, and Bell Laboratories, Murray Hill, NJ, USA. He is currently a Vice Rector for teaching with the University of Bologna. His current research interest includes device modeling. He has been the Chairman of the TCAD Technical Committee, and a member of several EDS committees.

GIUSEPPE CROCE was born in Messina, Italy, in 1969. He received the M.Sc. degree (summa cum laude) in electronic engineering from Pisa University, in 1994. He joined STMicroelectronics, in 1995, where he is currently a Technology Line Manager of smart power technology research and development organizations. He researched on the design and development of bipolar CMOS DMOS technology platform for consumer, industrial, and automotive applications. He has co-authored over ten papers and several patents.

**CLAUDIO FIEGNA** received the Ph.D. degree from the University of Bologna, Bologna, Italy. He is currently a Professor of Electronics with the University of Bologna. His research interests include numerical device simulation and its application to the analysis of advanced MOS device structures and silicon-based photovoltaic cells.