Novel TCAD Approach for the Investigation of Charge Transport in Thick Amorphous SiO2 Insulators / Giuliano F.; Reggiani S.; Gnani E.; Gnudi A.; Adsecti M. Depetto RI; Cloce C. NALETE TRANSACTIONS ON ELECTRON DEVICES TISSN 0018-9383. - ELETTRONICO - 68:11(2021), pp. 9507338.5438-9507338.5447. [10:1109/TED:2021.3100309] ELLA RICERCA

# Alma Mater Studiorum Università di Bologna Archivio istituzionale della ricerca

Novel TCAD Approach for the Investigation of Charge Transport in Thick Amorphous SiO2 Insulators

This is the final peer-reviewed author's accepted manuscript (postprint) of the following publication:

Published Version:

Availability: This version is available at: https://hdl.handle.net/11585/851993 since: 2022-02-03

Published:

DOI: http://doi.org/10.1109/TED.2021.3100309

Terms of use:

Some rights reserved. The terms and conditions for the reuse of this version of the manuscript are specified in the publishing policy. For all terms of use and more information see the publisher's website.

This item was downloaded from IRIS Università di Bologna (https://cris.unibo.it/). When citing, please refer to the published version.

(Article begins on next page)

This is the final peer-reviewed accepted manuscript of:

F. Giuliano *et al.*, "Novel TCAD Approach for the Investigation of Charge Transport in Thick Amorphous SiO2 Insulators," in *IEEE Transactions on Electron Devices*, vol. 68, no. 11, pp. 5438-5447, Nov. 2021

The final published version is available online at:

https://doi.org/10.1109/TED.2021.3100309

Rights / License:

The terms and conditions for the reuse of this version of the manuscript are specified in the publishing policy. For all terms of use and more information see the publisher's website.

This item was downloaded from IRIS Università di Bologna (<u>https://cris.unibo.it/</u>)

When citing, please refer to the published version.

# Novel TCAD approach for the investigation of charge transport in thick amorphous SiO<sub>2</sub> insulators

Federico Giuliano, Susanna Reggiani, Elena Gnani, Antonio Gnudi, Mattia Rossetti, Riccardo Depetro, Giuseppe Croce

Abstract—A TCAD approach for the investigation of charge transport in thick amorphous silicon dioxide is presented for the first time. Thick oxides are investigated representing the best candidates for integrated galvanic insulators in future power applications. The large electric fields such devices experience and the pre-existing defects in the amorphous material give rise to a leakage current which leads to degradation and failure. Hence it is crucial to have a complete understanding of the main physical mechanisms responsible for the charge transport in amorphous silicon oxide. For this reason, metal-insulator-metal structures have been experimentally characterized at different high-field stress conditions and a TCAD approach has been implemented in order to gain insight into the microscopic physical mechanisms responsible of the leakage current. In particular, the role of charge injection at contacts and charge build-up due to trapping-detrapping mechanisms in the bulk of the oxide layer have been investigated and modeled to the purpose of understanding the oxide behavior under DC and AC stress conditions. Numerical simulations have been compared against experiments to quantitatively validate the proposed approach.

Index Terms—Silicon oxide; Insulators; Reliability; TEOS;

# I. INTRODUCTION

Metal-insulator-metal (MIM) capacitors embedded in the back-end inter-level dielectric layers have been recently proposed for analog and RF applications [1]–[3]. Silicon dioxide (SiO<sub>2</sub>) is the main insulator in the electronics industry because of its near-ideal properties; however, ultimate device degradation and failure is still limited by charge buildup in defect sites of the oxide layer. Moreover, tetraethyl orthosilicate (TEOS) capacitors for galvanic insulation are complex structures made through several oxidation steps due to their large thickness subject to high electric fields [4]. The TEOS PE-CVD process is a low temperature deposition technique usually adopted for interlayer dielectrics. It allows to grow

Mattia Rossetti, Riccardo Depetro, Giuseppe Croce are with STMicroelectronics, Agrate Brianza, 20864, Italy (e-mail: mattia.rossetti@st.com; riccardo.depetro@st.com; giuseppe.croce@st.com). thick SiO<sub>2</sub> films, however the dielectric tends to show different electrical properties with respect to thermally grown SiO<sub>2</sub> [5], [6]. TEOS SiO<sub>2</sub> is known to provide a high leakage current due to a lower conduction band offset and is found to have a much larger density of preexisting defects. However, charge transport characterization and modeling has rarely been studied [5], [7]. Thus, charge build-up in the bulk of the oxide and charge injection at the contacts can significantly modify the electric field distribution across the device so that an undesired leakage current may arise that limits the device performance and reliability [8]. For this reason, a detailed knowledge of charge injection and transport mechanisms of such materials under high electric fields plays a key role in improving the reliability of such devices.

Concerning conduction, since very few free charges are present in the conduction band of an insulator at equilibrium, electrons usually are supplied by the cathode contact and a high electric field is necessary for an appreciable leakage current to flow through the insulator. Thus, transport in the oxide is usually referred to as injection-limited conduction [9], [10]. The most relevant mechanisms that give rise to injectionlimited current contribution are the thermionic emission, which consists in the classical emission over the metal-insulator barrier and the Fowler-Nordheim tunneling through the energetic barrier, which usually becomes relevant at high electric fields and usually is the most relevant contribution in  $SiO_2$  due to the quite high metal-insulator barrier.

A second important contribution to the leakage current in insulators is the so called bulk-limited current, which is due to a combination of ohmic conduction, space-charge limited current and trap-assisted conduction. In particular, emission mechanisms from traps, which can be either over the barrier (Poole-Frenkel emission) or under the barrier (pure tunneling or phonon-assisted tunneling), play an important role in amorphous materials like the TEOS SiO<sub>2</sub>.

Concerning defects, in the last decades trapping phenomena have been investigated by different experimental techniques and many different types of traps in  $SiO_2$  can be found in the literature [11]–[13]. Defects typically present in  $SiO_2$ have been extensively investigated also theoretically [14], [15]. However, it should be noted that the exact nature of the defects present in this material is process-dependent, so even if it was possible to have an overall estimation, it is difficult to deter-

Federico Giuliano (*corresponding author*), Susanna Reggiani, Elena Gnani, Antonio Gnudi are with the Department of Electrical Engineering (DEI) of the University of Bologna, Bologna, 40136, Italy (e-mail: federico.giuliano2@unibo.it; susanna.reggiani@unibo.it; elena.gnani@unibo.it; antonio.gnudi@unibo.it).

mine their energy levels and cross sections unambiguously. Moreover, the majority of the analyses on oxide traps in the literature address the role of defects in thin gate oxides which feature the presence of silicon at least at one side of the oxide layer, thus  $Si/SiO_2$  near-interface properties are investigated rather than bulk properties [16], [17]. Regarding bulk  $SiO_2$ , researchers have had to rely on theoretical calculations in order to determine the density distribution and position of the traps which are difficult to measure [18]–[20].

An example of modeling approach was shown in [7] where the tunneling current, the impact-ionization generation and the effect of capture and emission of traps were used to describe the leakage current characteristics of metal-insulator-silicon devices. As far as traps are concerned,  $Si/SiO_2$  interface traps were considered to be dominant with respect to  $SiO_2$  bulk ones. Interface traps were calibrated against thermally grown  $SiO_2$  and used to predict the leakage current of an annealed TEOS  $SiO_2$  showing very similar J-E characteristics. The nonannealed TEOS  $SiO_2$ , which is the subject of this study, was not simulated and no indications on the specific modeling of bulk traps, which are expected to play the main role in MIM structures, were reported in the work.

For such reasons, a TCAD-based comprehensive model of charge transport in oxides is highly desirable as it would be a key instrument for the development and optimization of ultracompact capacitances in integrated high-voltage systems. The TCAD framework would allow for the study of the full stack of materials once they are appropriately modeled. Thus, the goal of this work is to provide an efficient TCAD model for SiO<sub>2</sub> which captures the most important physical mechanisms responsible for the leakage current. For this purpose, we characterized thick back-end MIM structures in DC and AC regimes, we extrapolated the main transport features concerning traps and modeled them in a TCAD setup.

# **II. TEST STRUCTURES AND EXPERIMENTS**

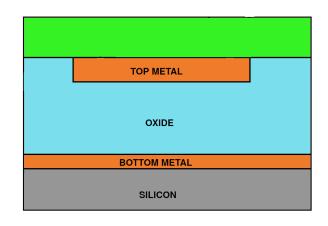

Fig. 1 shows a cross section of the high-voltage MIM capacitor used in this work. Two tantalium nitride (TaN) planar electrodes define the capacitance: the bottom metal is deposited on silicon and is grounded, the top metal is grown on top of the subsequential intermetal dielectrics forming the thick insulating region and is biased to positive/negative high voltages. TEOS processes are used for the oxide deposition. The nominal thickness of the capacitor is  $t_{OX} = 0.9 \ \mu m$ . The I-V characteristics of the MIM structure have been measured by applying a negative voltage to the top electrode. No relevant issues concerning with device variability were observed, thus the characteristics of single samples are used as references for the analyzed curves.

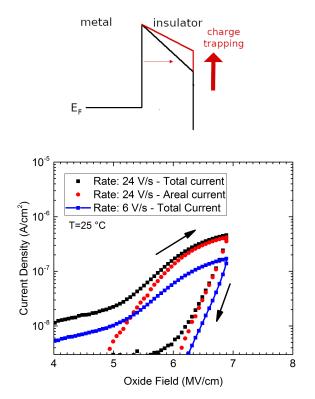

Contacts have a circular shape with a diameter  $d \approx 150$   $\mu$ m. Since  $d >> t_{\rm OX}$ , one can assume that the device behaves as a parallel plate capacitor. In order to validate this assumption, devices with different perimeter to area ratio have been measured to obtain the bulk and perimeter current densities at different biases. The comparison between the total current and the bulk contribution is reported in Fig. 2 where the current density is represented as a function of the applied

Fig. 1. Schematic view of the TEOS capacitor. The nominal thickness of the oxide is 0.9  $\mu\text{m}.$

electric field  $F_{\rm OX} = |V|/t_{\rm OX}$ , with V the voltage applied at the top electrode. At electric fields over 5.5 MV/cm, the bulk contribution dominates over the perimeter one. For this reason, the MIM structure can be modeled as a simple 1D planar capacitance neglecting the perimeter contribution to the current.

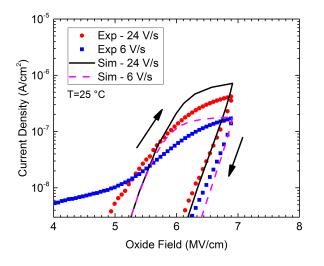

A forward and backward negative voltage ramp has been applied at the top metal with a relatively slow rate: it allows for the study of electron injection from top metal and of charge trapping effects. The negative bias applied allows us to study charge injection from the top contact. Measurements with two different ramp rates, namely 6 V/s and 24 V/s, have been performed to study the transient charge trapping. The voltage ramp rate has an impact on the filling probability of the traps due to the trapping time constants, which are proportional to the capture cross-sections [21]. A shorter sweeping can avoid or minimize injected carriers to be trapped leading to a larger injection current.

One can observe that the slower ramp of Fig. 2 features a significant reduction of the current density at high fields, which can be ascribed to a larger trapping with respect to the faster one. The slow current increase is mostly due to the electric field pinning due to charge trapping at the injecting electrode, reducing the tunneling through the barrier. A relevant hysteresis loop is observed in the curves of Fig. 2. The presence of a relevant hysteresis indicates that a great amount of charge has been trapped in the oxide and suggests that the energetic position of the trap levels is placed deep in the oxide band gap. In fact, the electron emission probability from shallower traps would be greater, giving rise to a larger current and resulting in a less pronounced (or even absent) hysteresis. Charge injection slightly changes between the forward and the backward ramp due to the trapped charge which can significantly modify the electric field distribution within the oxide and consequently the band diagram, as shown in the upper diagram of Fig. 2. The extracted bulk contribution is compared with the total one: a steep increase of the curves is shown at low fields, in accordance with the expected tunneling injection. The high current in the fast ramp at low fields is a hint that charge injection from the metal contact is dominant over charge trapping effects, which would significantly limit the current level. The lower current measured in the slow ramp case at higher electric fields ( $F_{\rm OX} > 5.5$  MV/cm) is ascribed to an enhanced charge trapping mechanism: the slower increase of the voltage bias allows a larger charge trapping within the oxide.

Fig. 2. **Top:** Oxide band diagram modifications due to the trapped charge. Charge trapping modifies the internal electric field distribution leading to different injection probabilities between the forward and the backward ramp.

**Bottom:** Measured current densities as a function of the electric field. Two voltage ramp-rates have been applied, namely 24 V/s and 6 V/s. For the faster ramp both the total measured current (squares) and the bulk contribution (circles) are represented.

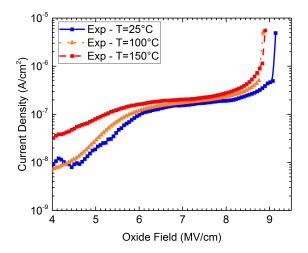

In order to gain insight on the contribution of the thermionic emission to the injected current, the slow ramp characteristics has been measured also at a temperature T = 100 °C and T = 150 °C. Fig. 3 shows the current curves measured at different temperature conditions from T = 25 °C to T = 150 °C. The temperature dependence is weak, with a limited shift at low electric fields where the injection contribution is expected to be the dominant one with respect to charge trapping as indicated by Fig. 2. Thus, the injected current by tunneling mechanisms plays the main role up to  $F_{OX} = 6$  MV/cm.

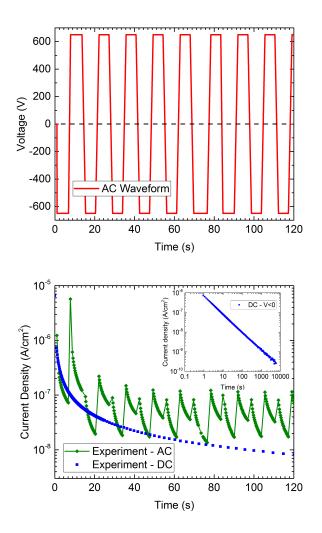

Finally, measurements under DC and AC stress conditions were carried out in order to assess the role of trapping/detrapping effects in such kind of structures (see Fig. 4). The negative DC voltage of -650 V is applied to the MIM stucture for a stress time up to  $10^4$  s. By observing the measured DC current in log scale (Fig. 4, inset) a decreasing curve was found, which can be ascribed to charge-trapping transient mechanisms depending on the characteristic capture cross-sections. The DC characteristics are strictly related to the

Fig. 3. Slow voltage ramp measurements at different temperature conditions up to breakdown: T = 25 °C, T = 100 °C and T = 150 °C.

trapping rate, i.e. the capture cross-sections and trap densities, as well as to the trap energy levels: the more charge is trapped, the faster the current will decrease over time. It can be used as a further verification of the calibration of trap parameters after the fitting of the voltage ramp characteristics.

The bipolar AC square voltage, with pulses of 650 V and period of 14 s (reported in the uppermost part of Fig. 4), is applied to the MIM under study for 120 s. The time delay of the first recorded point after the bias switch has been kept constant to 1 s for the duration of the measurement process. The recorded current transients are reported in Fig. 4, the first semiperiod is negative. In this case, the same trapping transient observed in the DC case appears at the beginning of the first semiperiod, followed by a relevant detrapping transient significantly increasing the current at the beginning of the positive semiperiod. A clear asymmetry is observed in the trapping transients, which can be ascribed to different metal/oxide interfaces for the top and bottom electrodes. An average current density at long stress times is found which seems to reach a regime condition in the last few periods.

We cannot exclude that defect generation may be present during the applied stress. However, the regular periodic behavior reached after the first few periods is a clear hint that the defects eventually generated at the longest stress times produce negligible effects in the current transients. Detrapping mechanisms show a fast recovery which needs to be accurately accounted for.

In the following, the  $SiO_2$  transport modeling is addressed by assuming the most relevant physical models and fixing their parameters using reference data from the literature (Section III). The experimental data reported here have been used as a reference to model and fit the bulk trap densities and their relative parameters, as detailed in Section IV.

#### III. MODELING APPROACH

The conduction model in amorphous materials can be described by using a drift-diffusion (DD) transport model with

Fig. 4. **Top:** AC stress applied voltage. The amplitude is 650 V and the period is 14 s.

**Bottom:** Current versus time semi-log plot of the AC (lines+symbols) and negative polarity DC (symbols) characteristics. The first semiperiod of the AC characteristics has negative polarity. Inset: log-log current plot of the DC measurements.

suitable physical parameters, such as the energy structure, the presence of distributed trap densities in the material band gap and proper boundary conditions, in order to correctly account for charge injection at the contacts [10], [22]. Trapping and detrapping mechanisms have been taken into account by using a first-order detailed balance equation for each trap as available in the TCAD tool [23]: the model explicitly takes into account the occupation rate of each trap by coupling the capture and emission rates to the conduction and valence band of the  $SiO_2$ . In order to properly account for the trapping and de-trapping effects, the Poisson equation is solved along with the transport and continuity equations of electrons and holes. The trapped charge is explicitly accounted for in the Poisson equation. This approach requires to explicitly define each type of defect, as it will be described in more details in the next section, by fixing their energy dependence, densities and capture crosse-sections. Any field-enhanced effect on the capture and emission rates has been assumed to be modeled in the capture cross-section of each trap. Hence, the DD transport equations for electrons,

holes, the trap rate equations for different traps and the Poisson equation have been calculated self-consistently on the full domain. The oxide region of interest was treated as wideband gap semiconductor with appropriate physical parameters, in order to simulate the generation, transport, and trapping of carriers.

The electronic structure of  $SiO_2$  has been intensively investigated experimentally and theoretically. In [24], the properties of thermal  $SiO_2$  on silicon were reported, showing that the band gap, according to the experiments on internal photoemission, can be as low as 8.06 eV [25].

Moreover, the theoretical band calculations show that the electron effective mass tensor is isotropic and the electron effective mass is equal to  $0.5 \text{ m}_0$ . The hole effective mass tensor, on the contrary, is anisotropic and shows two mass values, 1.3  $m_0$  (light holes) and 7.0  $m_0$  (heavy holes) [24]. For this reason, the energy gap, the density of states and the carriers effective masses in the conduction and in the valence band and the intrinsic hole and electron mobility of the semiconductor material have been modified and set to the known values for silicon oxide. The energy gap has been set to the commonly accepted value  $E_{\rm G} = 8.9$  eV [26], while the conduction and valence band density of states are  $N_{\rm C} = 9 \cdot 10^{18} \ {\rm cm}^{-3}$  and  $N_{\rm V} = 2.6 \cdot 10^{19} \text{ cm}^{-3}$ , respectively. However, given the recent works on TEOS indicating a possible reduction of the gap, we checked the role of the bandgap value by simulating the same devices with  $E_G = 8$  eV. As reported by [6], [38] experiments show that TEOS-based structures exhibit an energy barrier at the contact as low as 2.5 eV, leading to a significant increase of the leakage current with respect to thermally-grown SiO<sub>2</sub>. In our simulations the energy barrier at the contact has been kept fixed to 2.5 eV. Thus, no significant variations have been observed due to the specific value of  $E_G$ . Such quantities provide the amount of free charges in the bulk.

Mobile electrons and holes in SiO<sub>2</sub> exhibit significantly different mobilities. Hole mobility ranges from  $10^{-11}$  to  $10^{-4}$  $cm^2V^{-1}s^{-1}$  depending on electric field and temperature [27], [28], while electron mobility ranges from 20 to  $40 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ [29], [30], [31]. The transport of holes through the oxide is believed to be due to mechanisms such as trap-mediated valence band conduction or hopping transport by tunneling between localized trap sites in the  $SiO_2$  bandgap [32]. However, simplified drift-diffusion based models have been successfully used to approximate carrier transport in  $SiO_2$  films [33], [34]. As both contacts are metal electrodes forming a Shottky barrier with the oxide interface much lower for electrons than for holes, in this contribution electron injection is expected to dominate. This is confirmed by the numerical simulations showing negligible hole-injection current. We implemented constant mobility models for both electrons and holes, with the effective mobilities reported in I [22], [27].

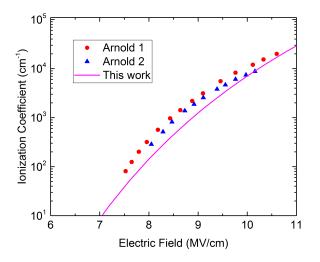

As far as high electric fields (up to 7 MV/cm) are concerned, impact ionization cannot be neglected if one wants to have a complete picture of the relevant physical mechanisms [35]. Thus, the impact-ionization generation has been taken into account in our simulation setup using the van Overstraeten-De Man model [36] fitted against the experimental and theoretical data in [35]. Fig. 5 shows the TCAD calibrated avalanche

#### TABLE I

TCAD parameter set for SiO<sub>2</sub> and TaN: metal Work Function ( $\Phi_m$ ), metal-oxide Energy barrier ( $E_B$ ), Energy bandgap ( $E_G$ ), conduction and valence band denstity of states ( $N_C$  and  $N_V$ ) and electron and hole mobility ( $\mu_e$  and  $\mu_h$ ) are reported.

| Parameter                                                  | Value              |

|------------------------------------------------------------|--------------------|

| $\Phi_{\rm m}~({\rm eV})$                                  | 4.4 [37]           |

| $E_{\rm B}~({\rm eV})$                                     | 2.5 [38]           |

| $E_{\rm G}~({\rm eV})$                                     | 8.9                |

| $N_{\rm C}~({\rm cm}^{-3})$                                | $9 \cdot 10^{18}$  |

| $N_{\rm V}~({\rm cm}^{-3})$                                | $2.6\cdot 10^{19}$ |

| $\mu_e \; (\mathrm{cm}^2 \mathrm{V}^{-1} \mathrm{s}^{-1})$ | 21                 |

| $\mu_h \ (\text{cm}^2 \text{V}^{-1} \text{s}^{-1})$        | $1 \cdot 10^{-4}$  |

coefficient against experimental data as a function of the electric field. The phonon energy was changed to 153 meV, consistently with the indications in [35] showing a limited temperature dependence of the impact-ionization generation in  $SiO_2$ . With such parameters, the full set of transient drift-diffusion equations was solved in the oxide region.

Fig. 5. Electron avalanche coefficient as a function of the electric field. Symbols: experimental data in [35]. Solid line: calibrated TCAD model.

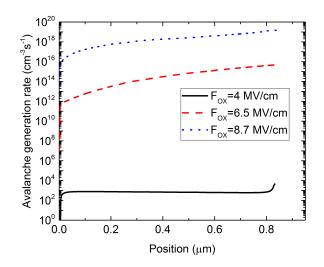

In fact, at high electric fields, a significant number of electron-hole pairs is generated by electron impact ionization, as reported in Fig. 6 in which it can be noted that in the intermediate-field regime ( $F_{\rm OX} = 6.5$  MV/cm) electron avalanche scattering rate is up to 10 orders of magnitude greater than its low-field regime ( $F_{\rm OX} = 4$  MV/cm) counterpart. At greater fields, namely  $F_{\rm OX} = 8.7$  MV/cm, the electron avalanche scattering rate is even greater and the ionization integral approaches the value of 1 corresponding to the breakdown condition.

Concerning charge injection from the electrodes, it has been properly taken into account by defining a Schottky barrier at the contacts with an energetic barrier  $E_{\rm B} = 2.5$  eV [38] and by calculating the tunneling probability of electrons using a nonlocal tunneling model based on the Wentzel-Kramers-Brillouin (WKB) approximation [23], [39]. The electron tunneling mass has been properly adjusted to 0.5 m<sub>0</sub>. Voltage

Fig. 6. Electron avalanche scattering rate as a function of the position across the device thickness at  $F_{0X} = 4$  MV/cm (low field regime),  $F_{0X} = 6.5$  MV/cm (intermediate field regime) and  $F_{0X} = 8.7$  MV/cm (high field regime).

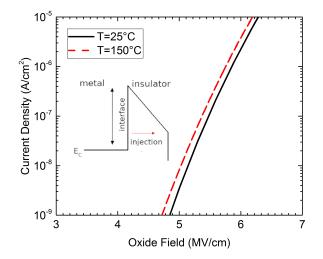

ramp simulations with ramp rate of 24 V/s with no traps have been performed at different temperatures in order to investigate charge injection at contacts. Fig. 7 shows the current density as a function of the applied electric field. The current temperature dependence is very weak, indicating that tunneling dominates over Schottky emission.

Fig. 7. Analysis of charge injection: current density as a function of the oxide field at two temperature conditions, namely T = 25 °C and T = 150 °C. Simulations have been performed with no traps. Inset: Metal-insulator band diagram.

As mentioned in the previous sections, despite the type of defects typically present in  $SiO_2$  are well known and extensively studied [14], many results can be applied only to very thin oxides featuring the presence of silicon at the interface.

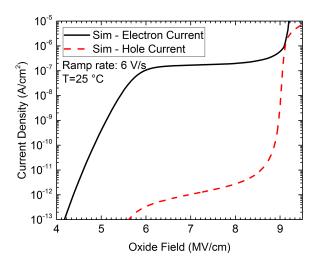

Both acceptor and donor traps are usually present in silicon

oxide. However, the implementation of both electron and hole traps would introduce many complications in our model and would make it much more difficult to handle. Anyway the injection of holes is negligible as shown in Fig. 8 where the electron and hole current densities are reported as a function of the applied electric field, thus only acceptor traps have been implemented.

Fig. 8. Electron and hole current densities as a function of the applied electric field from simulations for a voltage ramp stress with ramp rate of 6 V/s.

# IV. MAIN ROLE OF TRAPS

As far as electron trapping is concerned, we have defined only acceptor-type traps for electrons, i.e. defects that are neutral when empty and carry a negative charge when occupied by an electron. A uniform spatial distribution is assumed for all traps.

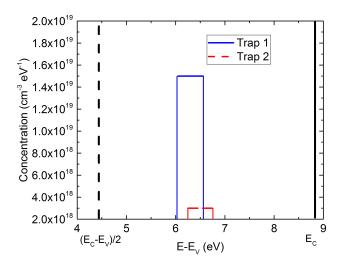

Concerning the energy level of the traps, it should be pointed out that, being SiO<sub>2</sub> an amorphous material, energy bands arise instead of discrete trap levels. For this reason we have defined two uniform distributions with a width of 0.5 eV each with mean energies  $E_1 = 6.3$  eV and  $E_2 = 6.5$ eV, where the oxide valence band has been taken as the reference level. These values are in quite good agreement with the results reported in [14] corresponding to the four-state hydrogen bridge and hydroxyl center defects, respectively. In Fig. 9 the energetic distribution of the traps is represented. The total net concentration of the two traps is  $N_1 = 7.5 \cdot 10^{18}$ cm<sup>-3</sup> for the deeper trap and  $N_2 = 1.5 \cdot 10^{18}$  cm<sup>-3</sup> for the shallower.

The determination of trap cross-sections requires a special attention for transient responses. In the past years, many authors have reported measurements of electron capture cross sections [40]–[44], with values ranging from  $10^{-13}$  cm<sup>2</sup> to  $10^{-18}$  cm<sup>2</sup>, so cross sections are not unambiguously determined. We have used two different cross sections of respectively  $\sigma_1 = 1.1 \cdot 10^{-15}$  cm<sup>2</sup> and  $\sigma_2 = 9 \cdot 10^{-15}$  cm<sup>2</sup>, in fair good agreement with the values reported in [45], where

Fig. 9. Energy distribution of traps. The valence band has been taken as the reference level, i.e.  $E_{\rm V}=0$ . The point  $(E_{\rm C}-E_{\rm V})/2$  represents the mid-band gap.

#### TABLE II

Trap parameters used for the two trap distributions. Mean energy of the trap level, trap width, electron capture cross section and trap density are reported for each type of trap. The parameter  $E_{\rm T}$  is referred to the top of the conduction band, taken as the reference level.

| Parameter                   | Trap 1               | Trap 2             |

|-----------------------------|----------------------|--------------------|

| $E_{\rm T}$ (eV)            | 6.3                  | 6.5                |

| $\Delta E$ (eV)             | 0.5                  | 0.5                |

| $\sigma_e ~(\mathrm{cm}^2)$ | $1.1 \cdot 10^{-15}$ | $9 \cdot 10^{-15}$ |

| $N_{\rm T}~({\rm cm}^{-3})$ | $7.5 \cdot 10^{18}$  | $1.5\cdot10^{18}$  |

it has been shown that two different electron cross sections exist which differ by as much as 1-2 orders of magnitude. This choice allows us to better describe the transient response of the DC stress characteristics on the full time range covering 4 orders of magnitude.

The second important aspect to take into account in order to have a complete representation of the physics of the device, is the definition of the field-enhanced emission mechanisms which play a relevant role at high fields. To this purpose, the cross-section is defined as a function of enhancement factors modeling the Poole-Frenkel effect and the Hurkx trap-assisted tunneling, both available in the TCAD tool [23]. As far as the Poole-Frenkel effect is concerned, the emission cross section enhancement factor is calculated as follows:

$$\Gamma_{\rm PF} = \frac{1}{\alpha^2} [1 + (\alpha - 1)e^{\alpha}] - \frac{1}{2}$$

(1)

$$\alpha = \frac{1}{kT} \sqrt{\frac{q^3 F}{\pi \varepsilon_0 \varepsilon_{\rm PF}}} \tag{2}$$

where F is the electric field, q is the electron charge, T the temperature and  $\varepsilon_{PF}$  the Poole-Frenkel permittivity of SiO<sub>2</sub>. It should be noted that the typical square-root dependence is valid only if one assumes a coulombic potential for traps [46], [47]. Other potentials lead in some cases to integrals

which cannot be solved analitically. By using this model we are implicitly assuming that we are dealing with a coulombic potential, which is a reasonable hypothesis.

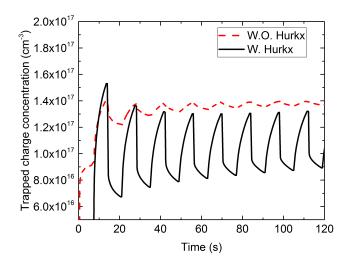

In addition to the Poole-Frenkel model, the emission due to tunneling at high fields, namely the Hurkx model [48], has been considered because at very high electric fields the tunneling from traps to the conduction band is not negligible and can dominate over the Poole-Frenkel emission [49]. Such effect is expected to play a key role in the AC stress conditions. This hypothesis has been checked by extracting the total trapped charge during a square-wave AC stress with pulses of 650 V and period of 14 s, where the impact of charge trapping and detrapping is supposed to be dominant. In Fig. 10 we report a comparison of the trapped charge near the top electrode between a simulation obtained by activating both the Hurkx and the Poole-Frenkel models and an analogous one in which only the Poole-Frenkel model has been used. It is clear that by activating the Hurkx model it is possible to have an appreciable charge de-trapping during the stress. Thus the Hurkx model implemented in Synopsys TCAD has been activated [48].

Fig. 10. Trapped charge concentration as a function of time for a square wave AC stress near the top contact. Continuous line: simulation performed activating the Hurkx model; Dashed line: simulation performed without the Hurkx model.

# V. TCAD ANALYSES OF THE EXPERIMENTAL RESULTS

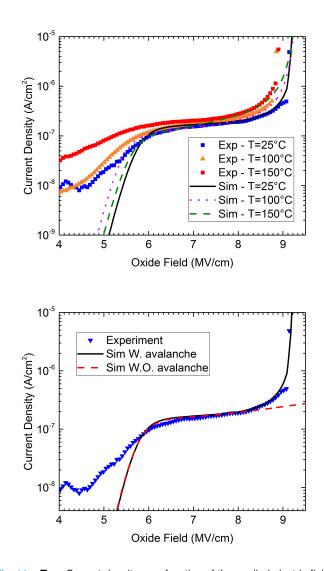

The TCAD results are compared against J-V experiments in different regimes to check the validity of the proposed transport model. Fig. 11 shows the slow voltage ramp stress current densities as a function of the applied electrical field up to breakdown at different temperatures, namely T = 25°C, T = 100 °C and T = 150 °C. The low-electric field part of the characteristics is strictly related to the charge injection due to tunneling effect. At intermediate electric fields the current is mainly limited by charge trapping effects: this indicates that the cathode field is decreasing due to significant electron trapping in the bulk of the oxide, which in turn limits the tunneling current. In the high-field regime, namely between 8 MV/cm and 10 MV/cm, one can notice the effect of impact ionization, as also shown in Fig. 11, bottom, where simulations without the avalanche generation are reported. The slight difference observed in the current levels at different temperatures in the intermediate fields regime can be ascribed to the effect of temperature on the trapping rates. However, the temperature dependence of the breakdown field due to impactionization generation is limited, as confirmed by the simulation lines crossing at a field of 9.2 MV/cm, consistently with the phonon energy of 153 meV [35].

Fig. 11. **Top:** Current density as a function of the applied electric field for voltage ramp stress up to breakdown. Three temperature conditions are represented, namely T = 25 °C, T = 100 °C and T = 150 °C. Symbols: experiments; Solid and dashed lines: simulations. **Bottom:** Current density as a function of the applied electric field for the voltage ramp stress up to breakdown at T = 25 °C. The experimental measures (symbols) are compared to simulations performed with the avalanche model (solid line) and without it (dashed line).

Concerning the faster ramp shown in Fig. 12, despite the peak current slightly differs from the experimental value (by about a factor of 2), the hysteresis is very well reproduced, indicating that the amount of trapped charge during the stress is in quite good agreement with the experimental data. Moreover, the slope of the decreasing part of the ramp is nicely captured by simulations. The low field deviation from the tunneling contribution might be due to defect-related conduction, as a trap assisted tunneling from contacts [5], [6]. However, at high fields the latter is not relevant with respect to the tunneling contribution. In the backward ramp the trap assisted tunneling is suppressed because traps are charged and the WKB tunneling behavior is observed.

Fig. 12. Current density as a function of the applied electric field for voltage ramp stress up to  $F_{\rm OX}=6.75$  MV/cm. Two ramp rates have been used, namely 24 V/s and 6 V/s. Symbols: experiments; Solid line: simulations.

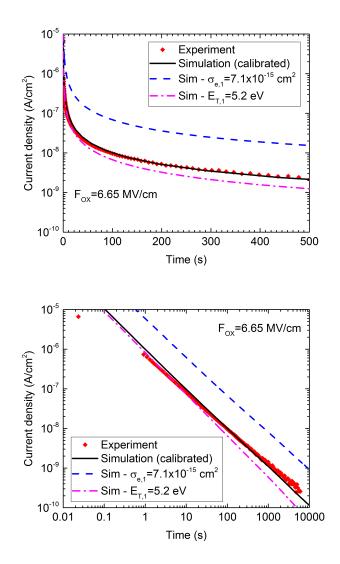

The trap parameters, such as energy distribution and cross section, can be investigated by analyzing the DC-stress characteristics. Fig. 13 show the current density versus time characteristics for the constant voltage stress at  $F_{OX} = 6.65$ MV/cm. Simulations with different sets of trap parameters are reported. The solid black lines of Fig. 13 are in fair good agreement with the experimental results. Changing either the mean energy of the traps or the electron capture cross section can have a great impact on the current, leading to a non correct prediction of experimental data. In particular, setting a smaller cross section for both traps (blue dashed curves of Fig. 13) leads to a nearly rigid shift of the log-log characteristics: the less charge is trapped, the greater the current will be. It should be noted that the slope of the straight line in the log-log plot is directly related to the traps depth within the energy bandgap of the insulator, as demonstrated by the dot-dashed curves of Fig. 13 which feature a modification of only the mean energy of the traps with respect to the best choice of trap parameters. Thus we can conclude that our choice of the energy levels can capture the relevant mechanisms.

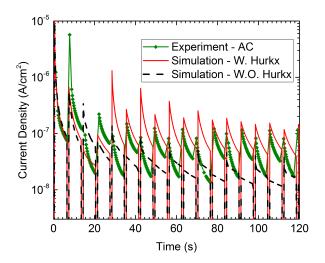

In order to assess the role of detrapping mechanisms, the AC-stress characteristics have been taken as the main reference. Fig. 14 shows the experimental versus simulated AC current characteristics obtained with two different setups: in the first one (dashed line of Fig. 14) the Poole-Frenkel model has been activated and the Hurkx model has been turned off; in the second one (solid line of Fig. 14) both

Fig. 13. **Top:** Semi-logarithmic current plot comparison of experimental data (symbols) and simulation results (solid and dashed lines) for a constant voltage stress performed at  $F_{0X} = 6.65$  MV/cm.

**Bottom:** Log-log current plot comparison of experimental data (symbols) and simulation results (solid and dashed lines) for a constant voltage stress performed at  $F_{0X} = 6.65$  MV/cm.

The black solid lines were obtained with the calibrated parameters for all the traps (reported in II), while the blue dashed and red dash-dotted lines were obtained by changing only the capture cross section and the trap level of the first trap, respectively.

models have been activated. The sole Poole-Frenkel model is not capable of reproducing the observed recovery of the current at each half-wave, which is strictly related to detrapping mechanisms. However, the current recovery can be at least qualitatively captured by activating also the Hurkx model for the emission cross section enhancement. This is a hint that trap-assisted tunneling is not negligible at the electric fields under consideration and has to be properly modeled as well as the Poole-Frenkel effect.

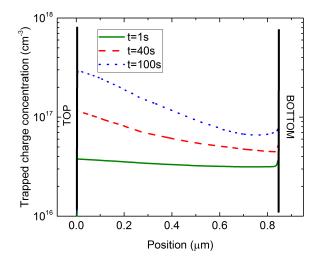

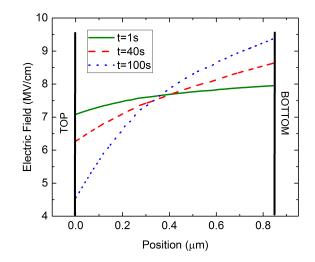

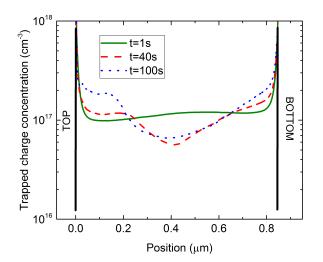

Finally, in order to gain further insight on the charge trapping and detrapping dynamics, Fig. 15 and 17 show the trapped charge across the device at different instant of the DC and AC transient simulations, respectively. For the DC

Fig. 14. Current density as a function time for a square wave AC stress with period T = 14 s and amplitude  $F_{0X} = 6.65$  MV/cm. Symbols+line: experiments; Solid lines: simulations with the Hurkx model; Dashed line: simulations without the Hurkx model.

stress condition, also the electric field distribution across the insulator has been reported in Fig. 16. The two stress conditions show very different behaviors. In the DC stress (Fig. 15), even if the great majority of the total charge is trapped in the first instants of the simulation, charge buildup in the oxide continues for hundreds of seconds up to a saturation condition. In addition, one can observe that more charge is trapped near the top contact, as expected, as it is the injecting contact thus causing charge accumulation in its proximity. As clearly shown by Fig. 16, the trapped charge is responsible for a consistent modification of the electric field, which increases near the the anode and decreases in proximity of the cathode contact. Differently, in the AC stress (Fig. 17) the saturation condition seems to be reached at shorter times with respect to the DC counterpart. Moreover, charge buildup is significantly enhanced near the two contacts, while a slight emptier region is formed in the center of the device. In fact, the two electrodes act in succession as injecting contacts leading to a greater charge trapping which is not possible in the center of the oxide due to a different balance between trapping and detrapping mechanisms.

## VI. CONCLUSIONS

A compact TCAD model has been presented to investigate conduction mechanisms in high-voltage silicon oxide thick TEOS capacitors for galvanic insulation. The most important conduction mechanisms, i.e. charge injection at the electrodes and trap-assisted capture and emission processes have been modeled in order to reproduce the electrical behavior of the device in different stress conditions: constant voltage stress, AC stress and voltage ramp. The role of traps has been extensively investigated. Despite it is not possible to determine unambiguously the exact nature of defects being silicon oxide an amorphous material and the type of traps being process-dependent, it has been shown that it is possible

Fig. 15. Trapped charge as a function of the position across the oxide layer for the DC-stress. Three instants are represented: t = 1 s (solid line), t = 40 s (dashed line), t = 100 s (dotted line).

Fig. 16. Electric field distribution across the oxide layer for the DC-stress. Three instants are represented: t = 1 s (solid line), t = 40 s (dashed line), t = 100 s (dotted line).

to reproduce the leakage current of thick capacitors with a proper choice of trap parameters such as concentration, crosssection and energy level. Numerical simulations have been nicely compared against experiments up to the breakdown regime validating the proposed approach, which can be used to study galvanic insulators in their high-field regime thus guiding design optimization of such devices.

#### ACKNOWLEDGMENT

#### REFERENCES

[1] C. C. Hung, A. S. Oates, H. C. Lin, P. Chang, J.L. Wang, C.C. Huang, and Y.W. Yau, *New understanding of Metal-Insulator-Metal (MIM) capacitor degradation behavior*, IEEE 45th Annual International Reliability Physics Symposium, Phoenix, AZ, USA, pp. 630-631, April 15-19, 2007. DOI: 10.1109/RELPHY.2007.369985.

Fig. 17. Trapped charge as a function of the position across the oxide layer for the AC-stress. Three instants are represented: t = 1 s (solid line), t = 40 s (dashed line), t = 100 s (dotted line).

- [2] P. Mahalingam, D. Guiling, S. Lee, *Manufacturing challenges and method of fabrication of on-chip capacitive digital isolators*, IEEE International Symposium on Semiconductor Manufacturing, Santa Clara, CA, USA, pp. 1-4, October 15-17, 2007. DOI: 10.1109/ISSM.2007.4446870.

- [3] R. Higgins, and J. McPherson, *TDDB Evaluations and Modeling of Very High-Voltage (10 KV) Capacitors*, IEEE 47th Annual International Reliability Physics Symposium, Montreal, QC, Canada, pp. 432-436, April 26-30, 2009. DOI: 10.1109/IRPS.2009.5173292.

- [4] S. Shin, Y.P. Chen, W. Ahn, H. Guo, B. Williams, J. West, T. Bonifield, D. Varghese, S. Krishnan, and M. A. Alam *High Voltage Time-Dependent Dielectric Breakdown in Stacked Intermetal Dielectric*, IEEE 56th Annual International Reliability Physics Symposium, Burlingame, CA, USA, pp. P-GD.9-1-P-GD.9-5, March 11-15, 2018. DOI: 10.1109/IRPS.2018.8353669.

- [5] W. Wu, S. Rojas, S. Manzini, A. Modelli, D. Re, *Characterization Of SiO<sub>2</sub> Films Deposited By Pyrolysis Of Tetraehylorthosilicate (TEOS)*, Journal de Physique Colloques, Vol. 49 (C4), pp.C4-397-C4-400, 1988. DOI: 10.1051/jphyscol:1988483.

- [6] M. Sometani, R. Hasunuma, M. Ogino, H. Kuribayashi, Y. Sugahara and K. Yamabe, *Suppression of Leakage Current of Deposited SiO2 with Bandgap Increasing by High Temperature Annealing*, ECS Transactions, Vol. 19 (2), pp. 403-413, 2009. DOI: 10.1149/1.3122105.

- [7] S. Kanitz, Charge transport in Thick SiO<sub>2</sub>-based dielectric layers, Solid-State Electronics, Vol. 41, No 12, pp. 1895-1902, 1997. DOI: 10.1016/S0038-1101(97)00163-9.

- [8] E.F. Runnion, S.M. Gladstone, R.S. Scott, D.J. Dumin, L. Lie, and J.C. Mitros, *Thickness Dependence of Stress-Induced Leakage Currents in Silicon Oxide*, IEEE Transactions On Electron Devices, Vol. 44, No. 6, pp. 993-1001, June 1997. DOI: 10.1109/16.585556.

- [9] T.H.Chiang and J.F.Wager, *Electronic Conduction Mechanisms in In-sulators*, IEEE Transactions On Electron Devices, Vol. 65, No. 1, pp. 223-230, Jan. 2018. DOI: 10.1109/TED.2017.2776612.

- [10] P. C. Arnett, *Transient conduction in insulators at high fields*, Journal of Applied Physics 46, pp. 5236-5243, 1975. DOI: 10.1063/1.321592.

- [11] P. M. Lenahan, and P. V. Dressendorfer, *Hole traps and trivalent silicon centers in metal/oxide/silicon devices*, Journal of Applied Physics 55, pp. 3495-3499, 1984. DOI: 10.1063/1.332937.

- [12] W.D.Zhang, J.F.Zhang, M.Lalor, D.Burton, G.V.Groeseneken and R.Degraeve, *Two Types of Neutral Electron Traps Generated in the Gate Silicon Dioxide*, IEEE Transactions On Electron Devices, Vol. 49, No. 11, pp. 1868-1875, Nov. 2002. DOI: 10.1109/TED.2002.804709.

- [13] J. F. Zhang, S. Taylor, and W. Eccleston, *Electron trap generation in thermally grown SiO<sub>2</sub> under Fowler–Nordheim stress*, Journal of Applied Physics, Vol. 71, pp. 725-734, 1992. DOI: 10.1063/1.351334.

- [14] W. Goes, Y. Wimmer, A.M. El-Sayed, G. Rzepa, M. Jech, A.L. Shluger, T. Grasser, Identification of oxide defects in semiconductor devices: A systematic approach linking DFT to rate equations and experimental

evidence, Microelectronics Reliability, Vol. 87, pp. 286-320, 2018. DOI: 10.1016/j.microrel.2017.12.021.

- [15] B.E. Deal, Standardized Terminology for Oxide Charges Associated with Thermally Oxidized Silicon, IEEE Transactions On Electron Devices, Vol. 27, No. 3, pp. 606-608, March 1980. DOI: 10.1109/T-ED.1980.19908.

- [16] E. H. Poindexter, G. J. Gerardi, M.-E. Rueckel, and P. J. Caplan Electronic traps and Pb centers at the Si/SiO<sub>2</sub> interface: Band-gap energy distribution, Journal of Applied Physics, Vol. 56, No. 10, pp. 2844-2849, 1984. DOI: 10.1063/1.333819.

- [17] J. M. M. de Nijs, K. G. Druijf, V. V. Afanas'ev, E. van der Drift, and P. Balk Hydrogen induced donor-type Si/SiO<sub>2</sub> interface states, Applied Physics Letters, Vol. 65, No. 19, pp. 2428-2430, 1994. DOI: 10.1063/1.112696.

- [18] D. A. Buchanan, M. V. Fischetti and D. J. DiMaria, *Coulombic and neutral trapping centers in silicon dioxide*, Physical Review B, Vol. 43, No. 2, pp. 1471-1486, Jan. 1991. DOI: 10.1103/PhysRevB.43.1471.

- [19] D.J. DiMaria and J.W. Stasiak, *Trap creation in silicon dioxide produced by hot electrons*, Journal of Applied Physics, Vol. 65, No. 6, pp. 2342-2356, 1989. DOI: 10.1063/1.342824.

- [20] Y. Nissan-Cohen, J. Shappir and O. Frohman-Bentchkowsky, *Dynamic model of trapping-detrapping in SiO*<sub>2</sub>, Journal of Applied Physics, Vol. 58, No. 6, pp. 2252-2261, 1985. DOI: 10.1063/1.335942.

- [21] Dieter K. Schroder, *Semiconductor Material And device Characterization*, John Wiley and Sons, Inc., Third Edition, 2006.

- [22] J.F. Verwey, E.A. Amerasekera and J. Bisschop, *The physics of SiO<sub>2</sub> layers*, Reports on Progress in Physics, Vol. 53, No. 10, pp. 1297-1331, 1990.

- [23] Synopsys Inc., Sentaurus Device User Guide M-2016.12, 2016.

- [24] S.S. Nekrashevich and V.A. Gritsenko, *Electronic Structure of Silicon Dioxide (A Review)*, Physics of the Solid State, Vol. 56, No. 2, pp. 207-222, Feb. 2014. DOI: 10.1134/S106378341402022X.

- [25] R. J. Powell and M. Morad, Optical absorption and photoconductivity in thermally grown SiO<sub>2</sub> films, Journal of Applied Physics, Vol. 49, pp. 2499-2503, 1978. DOI: 10.1063/1.325099.

- [26] V. Astašauskas, A. Bellissimo, P. Kuksa, C. Tomastik, H. Kalbe, W.S.M. Werner, *Optical and electronic properties of amorphous silicon dioxide by single and double electron spectroscopy*, Journal of Electron Spectroscopy and Related Phenomena, Vol. 241, pp. 1-7, 2020. DOI: 10.1016/j.elspec.2019.02.008.

- [27] R. C. Hughes, *Hole mobility and transport in thin SiO<sub>2</sub> films*, Applied Physics Letters, Vol. 26, pp. 436-439, 1975. DOI: 10.1063/1.88200.

- [28] O.L. Curtis, and J.R. Srour, *The multiple-trapping model and hole transport in SiO*<sub>2</sub>, Journal of Applied Physics, Vol. 48, No. 9, pp. 3819-3828, 1977. DOI: 10.1063/1.324248.

- [29] M. Turowski, A. Raman, M.L. Alles, D. Ball, M.P. King, R.A. Reed, and R.D. Schrimpf, *Effect of Carrier Transport in Oxides Surrounding Active Devices on SEE in 45nm SOI SRAM*, RADECS Proceedings, Seville, Spain, pp. 20-23, 2011. DOI: 10.1109/RADECS.2011.6131294.

- [30] E. Gnani, S. Reggiani, and M. Rudan, *Density of states and group velocity of electrons in SiO<sub>2</sub> calculated from a full band structure*, Physical Review B, Vol. 66, pp. 1-10, Nov. 2002. DOI: 10.1103/Phys-RevB.66.195205.

- [31] H.J. Fitting, J.U. Friemann, *Monte-Carlo Studies of the Electron Mobility* in SiO<sub>2</sub>, Physica Status Solid Applications, Vol. 69, pp. 349-358, Jan. 1982. DOI: 10.1002/pssa.2210690135.

- [32] F.B. McLean, H.E. Boesch Jr., and T.R. Oldham, *Electron-hole gener-ation, transport, and trapping in SiO*<sub>2</sub>, Chapter 3 in Ionizing Radiation Effects in MOS Devices and Circuits, T.P. Ma and P.V. Dressendorfer, Eds. New York Wiley, pp. 87-192, 1989.

- [33] C. Brisset, V. Ferlet-Cavrois, O. Mosseau, J. Leray, R. Escoffier, and A. Michez, *Two-Dimensional Simulation of Total-Dose Effects on NMOS-FET With Lateral Parasitic Transistor*, IEEE Transactions on Nuclear Science, Vol. 43, pp. 2651-2658, Dec. 1996. DOI: 10.1109/23.556849.

- [34] J-L. Leray, P. Paillet, V. Ferlet-Cavrois, C. Tavernier, K. Belhaddad, and O. Penzin, *Impact of Technology Scaling in SOI Back-Channel Total Dose Tolerance. A 2-D Numerical Study Using Self-consistent Oxide Code*, IEEE Transactions on Nuclear Science, Vol. 47, No. 3, p. 620-626, June 2000. DOI: 10.1109/23.856489.

- [35] D. Arnold, E. Cartier, and D. J. DiMaria, *Theory of high-field electron transport and impact ionization in silicon dioxide*, Physical Review B, Vol. 49, No. 15, pp. 10278-10297, Apr. 1994. DOI: 10.1103/Phys-RevB.49.10278.

- [36] R. van Overstraeten and H. de Man, Measurement of the Ionization Rates in Diffused Silicon p-n Junctions, Solid-State Electronics, Vol. 13, No. 1, pp. 583–608, May 1970. DOI: 10.1016/0038-1101(70)90139-5.

- [37] Y. Sugimoto, M. Kajiwara, K. Yamamoto, Y. Suehiro, D. Wang, and H. Nakashima, *Effective work function modulation of TaN metal gate on HfO<sub>2</sub> after postmetallization annealing*, Applied Physics Letters, Vol. 91, pp. 112105 1-4, 2007. DOI: 10.1063/1.2783472.

- [38] N. Bhat, Pushkar P. Apte, and K. C. Saraswat, *Charge Trap Generation in LPCVD Oxides Under High Field Stressing*, IEEE Transactions On Electron Devices, Vol. 43, No. 4, pp. 554-560, April 1996. DOI: 10.1109/16.485537.

- [39] F. Jimenez-Molinos, F. Gamiz, A. Palma, P. Cartujo, and J. A. Lopez-Villanueva, *Direct and trap-assisted elastic tunneling through ultrathin gate oxides*, Journal of Applied Physics, Vol. 91, No. 8, pp. 5116–5124, 2002. DOI: 10.1063/1.1461062.

- [40] T.H. Ning, *High-field capture of electrons by Coulomb-attractive centers in silicon dioxide*, Journal of Applied Physics, Vol. 47, No. 7, pp. 3203-3208, 1976. DOI: 10.1063/1.323116.

- [41] N.S. Saks, and M. G. Ancona, Determination of Interface Trap Capture Cross Sections Using Three-Level Charge Pumping, IEEE Electron Device Letters, Vol. 11, No. 8, pp.339-341, Aug. 1990. DOI: 10.1109/55.57927.

- [42] D. J. DiMaria, F. J. Feigl, and S. R. Butler, *Trap ionization by electron impact in amorphous Si0<sub>2</sub> films*, Applied Physics Letters, Vol. 24, No. 10, pp. 459-461, 1974. DOI: 10.1063/1.1655011.

- [43] P. Solomon, *High-field electron trapping in SiO*<sub>2</sub>, Journal of Applied Physics, Vol. 48, No. 9, pp. 3843-3849, 1977. DOI: 10.1063/1.324253

- [44] J. Albohn, W. Füssel, N. D. Sinh, K. Kliefoth and W. Fuhs, *Capture cross sections of defect states at the Si/SiO<sub>2</sub> interface*, Journal of Applied Physics, Vol. 88, No. 2, p. 842-849, June 2000. DOI: 10.1063/1.373746.

- [45] M.H. Chang, J.F. Zhang, and W.D. Zhang, Assessment of Capture Cross Sections and Effective Density of Electron Traps Generated in Silicon Dioxides, IEEE Transactions On Electron Devices, Vol. 53, No. 6, pp. 1347-1354, June 2006. DOI: 10.1109/TED.2006.874155.

- [46] P. A. Martin, B. G. Streetman, and K. Hess, *Electric field enhanced emission from non-Coulombic traps in semiconductors*, Journal of Applied Physics, Vol. 52, No. 12, pp. 7409-7415, 1981. DOI: 10.1063/1.328731.

- [47] E. Rosencher, V. Mosser, and G. Vincent, *Transient-current study of field-assisted emission from shallow levels in silicon*, Physical Review B, Vol. 29, No. 3, pp. 1135-1147, Feb. 1984. DOI: 10.1103/Phys-RevB.29.1135.

- [48] G. A. M. Hurkx, D. B. M. Klaassen, and M. P. G. Knuvers, A New Recombination Model for Device Simulation Including Tunneling, IEEE Transactions On Electron Devices, Vol. 39, No. 2, pp. 331-338, Feb. 1992. DOI: 10.1109/16.121690.

- [49] G. Vincent, A. Chantre, and D. Bois, *Electric field effect on the thermal emission of traps in semiconductor junctions*, Journal of Applied Physics, Vol. 50, No. 8, pp. 5484-5487, 1979. DOI: 10.1063/1.326601.