# Role of the GaN-on-Si Epi-Stack on $\Delta R_{\text{on}}$ **Caused by Back-Gating Stress**

M. Millesimo<sup>®</sup>, M. Borga<sup>®</sup>, L. Valentini<sup>®</sup>, *Graduate Student Member, IEEE*, B. Bakeroot<sup>®</sup>, N. Posthuma<sup>®</sup>, A. Vohra<sup>(D)</sup>, S. Decoutere<sup>(D)</sup>, C. Fiegna, and A. N. Tallarico<sup>(D)</sup>, *Senior Member, IEEE*

Abstract—This article reports an in-depth analysis of the on-resistance drift ( $\Delta R_{ON}$ ) induced by storage/release mechanisms occurring in the buffer of GaN-on-Si power devices. The role of both stress condition (bias, temperature, and stress time) and buffer's epi-stack composition on  $\Delta R_{ON}$  has been analyzed by means of back-gating current deep-level transient spectroscopy (I-DLTS). The results reveal two competing mechanisms: 1) a faster one related to acceptor defects and sensitive to the thickness of the carbon-doped GaN back-barrier (C:GaN) and superlattice (SL) layers and 2) a slower one ascribed to hole accumulation at the C:GaN/SL interface, independent of the thickness of the epi-stack. The temperature, stress bias, and stress time dependence of such mechanisms, often overlapping, have been investigated by adopting a genetic algorithm.

Index Terms-AlGaN/GaN HEMT, back-gating current deep-level transient spectroscopy (I-DLTS), buffer trapping, *R*<sub>ON</sub> drift, stretched exponential.

#### I. INTRODUCTION

T IS well-known that the deposition of GaN and its compounds (AlGaN, AlN, etc.) on a foreign substrate (e.g., silicon) implies the presence of defects/dislocations along the entire buffer up to the device surface [1]. Even though, process engineering is at an advanced stage, and GaN-on-Si devices demonstrate a good capability of withstanding

Manuscript received 17 July 2023; accepted 7 August 2023. Date of publication 21 August 2023; date of current version 22 September 2023. This work was supported in part by Intelligent Reliability 4.0 (iRel40), iRel40 is a European co-funded innovation project that has been granted by the Electronics Components and Systems for European Leadership (ECSEL) Joint Undertaking (JU) under Grant 876659; in part by the Horizon 2020 Research Programme and participating countries; and in part by National Funding which is provided by Germany, including the Free States of Saxony and Thuringia, Austria, Belgium, Finland, France, Italy, The Netherlands, Slovakia, Spain, Sweden, and Turkey. The review of this article was arranged by Editor W. Saito. (Corresponding author: M. Millesimo.)

M. Millesimo, L. Valentini, C. Fiegna, and A. N. Tallarico are with the Advanced Research Center on Electronic System, Department of Electrical, Electronic, and Information Engineering, University of Bologna, 47522 Cesena, Italy (e-mail: maurizio.millesimo2@unibo.it; Lorenzo. valentini13@unibo.it; claudio.fiegna@unibo.it; a.tallarico@unibo.it).

M. Borga, N. Posthuma, A. Vohra, and S. Decoutere are with imec vzw, B-3001 Leuven, Belgium (e-mail: Matteo.Borga@imec.be; Niels.Posthuma@imec.be; Anurag.Vohra@imec.be; Stefaan. Decoutere@imec.be).

B. Bakeroot is with imec vzw. B-3001 Leuven. Belgium, and also with the Centre for Microsystems Technology, imec and Ghent University, B-9052 Ghent, Belgium.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2023.3304272.

Digital Object Identifier 10.1109/TED.2023.3304272

relatively high drain biases [2], [3], [4], [5], charge storage and release from buffer traps or in the overall stack is still one of the dominant mechanisms causing static and/or dynamic  $\Delta R_{\text{ON}}$  [6], [7], [8], [9], [10], [11], [12], [13]. Therefore, more effort is required to understand the origin of such mechanisms and how to optimize the buffer stack to minimize their effects.

In most cases, the C:GaN layer plays a key role in  $\Delta R_{\rm ON}$  since it can lead to charge storage and release during high-voltage OFF-state operation. According to the "leaky dielectric" model [6], when the buffer stack is exposed to a vertical electric field, two mechanisms show up: 1) the ionization of carbon-related acceptor traps (C<sub>N</sub>), promoting the storage of negative charge in the C:GaN layer, inducing  $R_{\rm ON}$  increase and 2) electron band-to-band tunneling from C:GaN valence band (VB) to two-dimensional electron gas (2DEG) through defects and dislocations, inducing hole accumulation at the C:GaN/superlattice (SL) interface, increasing the 2DEG density ( $R_{ON}$  decrease). In [13], it is shown that charge propagation through the C:GaN and the unintentional doped (uid)-GaN are assisted by 1-D and 3-D variable range hopping, respectively.

Many experimental techniques have been developed to investigate charging and discharging processes in the AlGaN/GaN buffers of power devices [12], [13], [14], [15], [16], [17], [18], [19], [20], [21]. Among them, one of the most adopted is the back-gating current deep-level transient spectroscopy (I-DLTS) [12], [13], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27], which consists in monitoring the recovery of  $R_{\rm ON}$  after a negative substrate voltage stress. The latter induces different charge storage mechanisms which may compete with each other making it difficult to distinguish and quantify their effect separately [12], [13], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], [24], [25], [26], [27]. In fact, the choice of the test conditions and the transient analysis technique can strongly impact the extracted parameters (e.g., activation energy) that characterize the kind of traps or the involved physical mechanisms [12]. The most accurate method consists in fitting the  $\Delta R_{\rm ON}$  as a sum of stretched exponentials, providing useful information to understand and quantify the role of the stress conditions on the trapping and storage mechanisms and their features [24], [25], [26], [27].

In this work, we adopted the back-gating I-DLTS technique to explore how the test conditions (substrate bias, stress time, and temperature) and the thickness of the layers composing

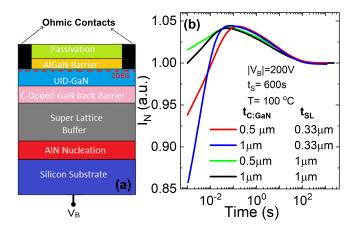

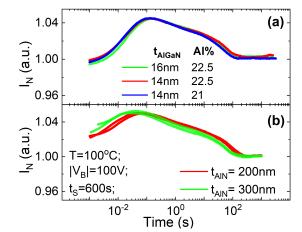

Fig. 1. Sketch (not to scale) of the device under test and the epi-structure. (a) Recovery current transient for different buffer configurations. (b) Stressing phase has been performed for 600 s with  $|V_B| = 200 \text{ V}$  at T = 100 °C.

the buffer epi-stack impacts on  $\Delta R_{\text{ON}}$ . The latter is fitted with a stretched exponential model by means of a mathematical approach, based on the study of the derivative, combined with a genetic algorithm to minimize the fitting error.

# **II. EXPERIMENTAL DETAILS**

A sketch of the devices under test (DUTs), fabricated by IMEC on 200-mm Si substrate for low-voltage HEMTs (<100 V), is shown in Fig. 1(a). The main difference with respect to GaN HEMT lies in the absence of the gate region. In this case, a passivation region is deposited on top of the AlGaN barrier and two ohmic contacts are created. Such a structure allows focusing the analysis directly on the buffer region, avoiding possible gate overdrive-dependent trapping mechanisms. The process splits on layers' thicknesses have been analyzed. The reference structure features an epi-stack composed of a 200-nm-thick AlN nucleation layer grown on top of Si-substrate, 330-nm-thick SL layer, 500-nm-thick C:GaN layer, 200-nm-thick uid-GaN channel layer, and 11-nm-thick Al<sub>0.23</sub>GaN<sub>0.77</sub> barrier layer.

The back-gating I-DLTS test consists of three consecutive steps: 1) the fresh current ( $I_0$ ) between the two ohmic contacts [see Fig. 1(a)] is measured with an applied voltage drop of 0.7 V and  $V_B = 0$  V; 2) a negative substrate stress voltage ( $V_B$ ) is applied for a fixed stress time ( $t_S$ ); and 3) the current between the two ohmic contacts is monitored under the same electrical conditions reported in 1) until the recovery is completed. Finally, the current monitored during step 3) is normalized ( $I_N$ ) with respect to the fresh value measured in 1). The reason why the current is monitored during the recovery rather than the stress phase is related to 2DEG depletion, which occurs for  $|V_B| > 50$  V, making the current monitoring difficult and noisy. Experiments have been performed at different temperatures, stress times, and  $V_B$ .

# **III. BRIEF PHYSICAL BACKGROUND**

Fig. 1(b) reports  $I_{\rm N}$  after a stress phase of 600 s with  $|V_{\rm B}| = 200$  V and T = 100 °C for all the process splits considered in this work. The current features two consecutive transients,

i.e.,  $I_N$  increase followed by a decrease toward the prestress value. For the sake of clarity, from here on, the faster (first) transient and the slower one (second) will be referred to as TR1 and TR2, respectively. In [11], the  $I_N$  increase is ascribed to electron detrapping from acceptor states in the C:GaN layer, which leads to a gradual increase of the 2DEG density (*R*on decrease), whereas TR2 is associated with recombination of holes accumulated at the C:GaN/SL heterointerface, inducing an  $R_{ON}$  increase (2DEG decrease). More details on the physical mechanisms can be found in [6], [7], [8], [9], [10], and [11]. It is worth noting that this description refers to the recovery phase; exactly the opposite occurs during the stress phase, i.e., electron trapping in acceptor states and hole accumulation at the C:GaN/SL interface, leading to  $R_{ON}$  increase and decrease, respectively.

#### IV. TRANSIENTS ANALYSIS METHODOLOGY

The adopted methodology is based on the stretched exponential fitting law [24], by approximating  $I_N$  as follows:

$$I_{\rm fit}(t) = 1 + \sum_{i=1}^{N} f_i(t) = 1 + \sum_{i=1}^{N} A_i e^{-\left(\frac{t}{\tau_i}\right)^{\beta_i}}$$

(1)

$f_i(t)$  is the *i*th stretched exponential, N is the number of involved charge/discharge processes,  $A_i$  is the transient amplitude representing the amount of stored/released charge,  $\tau_i$  is the charge emission time constant, and  $\beta_i$  is a stretching term representing the "slope" of the transient. The *i*th derivative is

$$f_i'(t) = -\frac{A_i \beta_i}{t} \left(\frac{t}{\tau_i}\right)^{\beta_i} e^{-\left(\frac{t}{\tau_i}\right)^{\beta_i}}.$$

(2)

To estimate  $\tau_i$  and simplify the computation, we define  $\psi_i(t)$  as

$$\psi_{i}(t) = \ln(10)tf_{i}'(t) = -\ln(10)A_{i}\beta_{i}\left(\frac{t}{\tau_{i}}\right)^{\beta_{i}}e^{-\left(\frac{t}{\tau_{i}}\right)^{\beta_{i}}} \quad (3)$$

to verify that maxima or minima of  $\psi_i(t)$  is located at  $t = \tau_i$ . Then, the triplet  $(A_i, \beta_i, \text{ and } \tau_i)$  can be retrieved as

$$\hat{\tau}_i = \max\{\psi_i(t)\} \text{ or } \hat{\tau}_i = \min\{\psi_i(t)\}$$

(4)

$$\hat{A}_i = e f_i \left( \hat{\tau}_i \right) \tag{5}$$

$$\hat{\beta}_i = -\frac{e}{\ln(10)} \frac{\psi_i(\hat{\tau}_i)}{\hat{A}_i}.$$

(6)

The question arises whether the estimation of  $A_i, \beta_i$ , and  $\tau_i$  parameters is correct or not by following this approach. By assuming that  $\tau_1 \ll \tau_2 \ll \cdots \ll \tau_N$ , the proposed method searches for the maxima and/or minima of the logarithmic derivative of f(t) given by  $\psi(t) = \sum_{i=1}^{N} \psi_i(t)$  obtaining preliminary estimations  $(\hat{\tau}_1, \hat{\tau}_2, \dots, \hat{\tau}_N)$ . Since  $\tau_1 \ll \tau_2 \ll \cdots \ll \tau_N$ , it is possible to approximate  $I_N(\tau_i)$  as

$$I_N(\hat{\tau}_i) \approx 1 + \frac{A_i}{e} + \sum_{k=i+1}^N A_k \tag{7}$$

for all i = 1, ..., N. Solving the linear system described in (7), estimates of  $A_1, A_2, ..., A_N$  can be obtained. Lastly,  $\beta$  coefficients can be estimated by using (6).

By observing Fig. 1(b), the number of transients is N = 2, and the solution is a set  $p = [A_1, \tau_1, \beta_1, A_2, \tau_2, \beta_2]$  of fitting

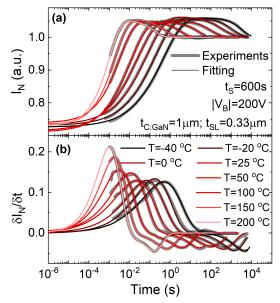

Fig. 2. (a) Recovery current transient and (b) its derivative with different temperatures ranging between -40 °C and 200 °C. The stressing phase has been performed for 600 s with  $|V_B| = 200$  V.

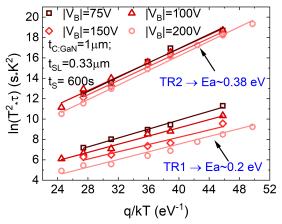

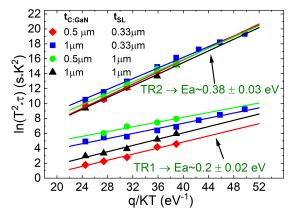

Fig. 3. Arrhenius plot in the case of stress voltage  $V_{\rm B} = -75, -100, -150,$  and -200 V, with a stress time of 600 s.

parameters with constraints  $A_1 < 0$ ,  $A_2 > 0$ ,  $\tau_1 < \tau_2$ , and  $\beta_i \in [0, 1]$ .

The criticality lies in the accuracy of (7), which is ensured only if  $\tau_1$  and  $\tau_2$  are significantly different from each other. In addition, even if the current transients are nicely reproduced,  $\psi_i(t)$  may not match the actual derivative. To get rid of such issues, the preliminary estimation is used as an initial solution of an optimizing algorithm, which minimizes an error function defined as the sum of the root-mean-square error (rms) of  $I_N(t)$ and its logarithmic derivative [29]

$$E = \sum_{j=1}^{N_{\text{samples}}} |I_{N_{\text{fit}}}(t_j; \hat{P}) - I_N(t_j)|^2 + |\psi_{\text{fit}}(t_j; \hat{P}) - \psi(t_j)|^2.$$

(8)

The goal of such an algorithm is to find the optimal set of parameters p providing the best fit of the transients and their derivatives. This is possible by using a differential evolution algorithm [29], [30], i.e., a metaheuristic method that

iteratively reduces E by evolving a population of approximate solutions accordingly to genetic algorithm methodology [31].

An initial population of vectors is generated by adopting the methodology described in this section. Then, a competitor (different possible solution) for each parameter vector under test is constructed by mutation and crossover over the current population. Each population element is compared with its own competitor and only one is selected (i.e., the one with the lower error), resulting in an evolved population. Finally, the mutation, crossover, and selection steps are iterated until the genetic algorithm is unable to generate a solution with a smaller error. This tool finds several applications in telecommunication systems, such as the optimization of low-density parity-check (LDPC) codes degree profile [32] and the design of coded random access protocols [33].

# V. ROLE OF THE TEST CONDITIONS A. Temperature Dependence

Fig. 2(a) and (b) shows  $I_N$  and its derivative, respectively, in the case of  $|V_{\rm B}| = 200$  V, stress time  $t_{\rm S} = 600$  s, and temperature ranging from -40 °C to 200 °C. Such  $t_{\rm S}$ , widely adopted for this study, has been chosen to: 1) allow a saturation of TR2 for any  $V_{\rm B}$  and 2) avoid causing permanent degradation. As observed, the methodology described in Section IV guarantees a good fitting, also in the case of high temperatures where the two transients are superimposed. Similar analyses have been performed also with different  $|V_{\rm B}|$ , i.e., 75, 100, and 150 V. Both transients TR1 (ascending) and TR2 (descending) show a clear temperature dependence, suggesting the presence of thermally activated charging/discharging processes with an activation energy  $(E_A)$ of 0.2 and 0.38 eV, respectively (Fig. 3). Such values are similar to the ones extrapolated in [13], [19], [34], and [35] by means of back-gating measurements on AlGaN/GaN buffers.

In the case of TR1, its ascending trend may be ascribed to electron emission from acceptor traps in C:GaN layer, as reported in [6], [11], and [12]. In [36], [37], and [38],  $E_{\rm A} = 0.2$  eV has been ascribed to carbon atoms occupying substitutional position on nitrogen sites (C<sub>N</sub>), leading to the creation of acceptor shallow traps with  $E_{\rm A}$  between 0.08 and 0.29 eV from VB. However, more recent studies [39], [40] report that the C<sub>N</sub> acceptors in GaN bulk are energetically located at 0.9 eV from VB. In such a case, the adoption of a relatively high carbon concentration ( $\sim 10^{19}$  in this case) determines a Fermi level position slightly lower than the one of C<sub>N</sub>, forcing the occupation of any possible preexisting acceptor states (assuming lower concentration with respect to C<sub>N</sub>) with energy level below the Fermi one. This has been confirmed by TCAD simulation (not shown). Consequently, it is more plausible that the extrapolated  $E_A = 0.2$  eV is not ascribed to the trap itself, but it represents the activation energy of trap-assisted charge transport in a defect band, probably centered at 0.9 eV from VB, i.e., carbon-related. In [13], a 3-D hopping via a defect band mechanism has been proposed. Additional discussion, supported by TCAD simulations, will follow in Section VI.

Regarding TR2,  $E_A = 0.38$  eV might be associated with donor-like defects such as C<sub>GA</sub> [41], oxygen [42], or silicon

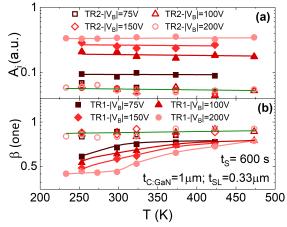

Fig. 4. Temperature dependence of the: (a) amplitude  $A_i$  and (b) stretching parameter  $\beta_i$  and for the two transient TR1 and TR2. Parameters have been extrapolated from measures reported in Fig. 2.

Fig. 5. Stressing voltage dependence of  $A_i$  for: (a) TR1 and (b) TR2.

[19] impurities. However, most likely, such value is not related to a defect itself but it could represent the energy of a charge-transport mechanism leading to electron–hole recombination among excess 2DEG electrons and holes accumulated at the C:GaN/SL heterojunction during the stress phase [13].

Fig. 4(a) and (b) shows the temperature dependence of the stretched exponential fitting parameters A and  $\beta$ , respectively. A is temperature-independent in both transients TR1 and TR2 [Fig. 4(a)], suggesting that the amount of charge trapped (TR1) and accumulated (TR2) during the stress is temperature-independent; it can be faster or slower but the quantity is only bias-dependent (detailed in the next section). Regarding  $\beta$ , a T-dependence is shown in the case of TR1, i.e., the higher T the higher  $\beta_1$ , while  $\beta_2$  (TR2) is almost independent, suggesting two distinct mechanisms and strengthening the theory reported in [13], i.e., electron detrapping from acceptor states (TR1) and recombination of the accumulated hole density at the C:GaN/SL interface (TR2).

#### B. Substrate Stress-Bias Dependence

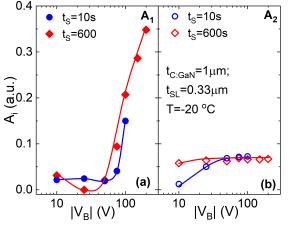

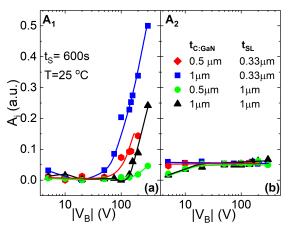

To investigate the  $V_{\rm B}$  dependence of the two transients, tests have been performed at T = -20 °C in order to have TR1 and TR2 quite distant from each other and to measure a bigger excursion of TR1. Fig. 5(a) shows the amplitude  $A_1$  of TR1 as a function of  $|V_{\rm B}|$ . Two regimes can be observed. For  $|V_{\rm B}| \le 50$  V,  $A_1$  is roughly constant and quite small, smaller than

Fig. 6. Stressing voltage dependence of: (a) stretching term  $\beta$  and (b) trap emission time for both transients.

$A_2$  [Fig. 5(b)]. In this region, the electron trapping during the stress can be compensated and/or perturbed by the mechanism inducing hole accumulation at the C:GaN/SL interface, i.e., band-to-band electron tunneling from C:GaN VB to 2DEG. Electrons tunneling releases free holes in the VB, which can accumulate at the C:GaN/SL interface as free charge or neutralize the acceptor states [6], opposing the increase of  $A_1$ . For  $|V_{\rm B}| > 50$  V,  $A_2$  saturates (also for short  $t_{\rm S}$ ) while  $A_1$ increases with  $|V_{\rm B}|$  becoming bigger than  $A_2$ . In this regime, on the one hand, leakage can start to flow through the entire epi-stack, electrons are injected from the substrate, and hole accumulation at the C:GaN/SL interface saturates, as well as  $A_2$ . On the other hand, more electrons can be trapped in the C:GaN layer because of the higher electric field, increasing  $A_1$ . The latter mechanism is further supported by TCAD simulations reported and discussed in the next section.

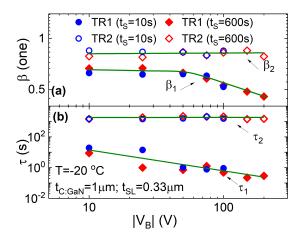

Fig. 6(a) reports the  $V_{\rm B}$ -dependence of  $\beta$ .  $\beta_1$  decreases by increasing  $|V_B|$ , except for low  $|V_B|$ , whereas  $\beta_2$  is biasindependent. As reported in [20], when the stretched exponential model is adopted to fit the effects of trapping/detrapping mechanisms,  $\beta$  can represent the energy window of the trap involved in the mechanisms. A value close to 1 implies that the trap behaves like a point defect with a discrete energy level, whereas a smaller  $\beta$  is associated with trapping centers forming a continuous distribution of energy levels. Based on this assumption, the smaller  $\beta_1$  by increasing  $|V_B|$ , reported in Fig. 4, may be the result of charge trapping during the stress in a wider energy window centered at  $\sim 0.9$  eV. On the contrary, the lack of  $V_{\rm B}$ -dependence of  $\beta_2$  further supports that TR2 is not linked to charge detrapping mechanisms but to the recombination of holes accumulated at the C:GaN/SL interface. The two mechanisms are further supported by the  $V_{\rm B}$ -dependence of  $\tau_1$  and  $\tau_2$  reported in Fig. 6(b). Also in this case,  $\tau_1$  is stress bias-dependent while  $\tau_2$  is not, confirming and excluding trapping/detrapping mechanisms for TR1 and TR2, respectively.

# C. Stress Time Dependence

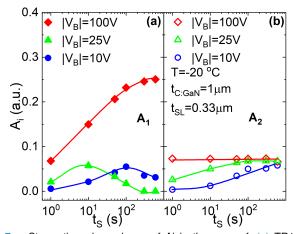

Fig. 7 reports the stress time dependence of the  $A_i$  parameters for three different  $V_{\rm B}$ . As anticipated in Section V-B, as long as  $A_1$  is smaller than  $A_2$  ( $|V_{\rm B}| < 50$  V), the trend of  $A_1$  with both stress bias [Fig. 5(a)] and stress time [Fig. 6(a)]

Fig. 7. Stress time dependence of Ai in the case of: (a) TR1 and (b) TR2. The temperature is -20 °C.

Fig. 8. Stress time dependence of: (a) stretching parameter and (b) trap emission time for both transients. The temperature is -20 °C.

is not monotonous because of the two competing mechanisms occurring during the stress phase, i.e., ionization and neutralization of acceptor states in the C:GaN layer, caused by the electric field and by free hole releasing (electron band-to-band) in the VB, respectively. Nonmonotonic  $R_{ON}$  drift has also been reported in [43].

For  $|V_{\rm B}| > 50$  V,  $A_2$  is already saturated while  $A_1$  increases hinting at a saturation for relatively long stress times (~600 s with  $|V_{\rm B}| = 100$  V), which is a typical behavior observed for trapping mechanisms in preexisting defects.

Finally, as expected, the stress time has no impact on  $\beta$  and  $\tau$ , as reported in Fig. 8(a) and (b), respectively.

# VI. ROLE OF THE BUFFER STACK COMPOSITION

Once the role played by the stress conditions is investigated, structures featuring different epi-stacks have been analyzed and compared. Fig. 9(a) shows  $I_N$  in the case of structures featuring different AlGaN barrier configurations in terms of thickness and aluminum content (Al%). As observed, both do not significantly impact on, confirming that the underneath mechanisms do not originate from the AlGaN barrier and its interfaces. Fig. 9(b) reports the same analysis carried out on structures with different AlN nucleation layer thicknesses. A negligible impact is shown also in this case, excluding such layer as location of trapping/accumulation mechanisms.

Fig. 9. Dependence of  $I_N$  in the case of: (a) different AlGaN barrier configurations and (b) AlN thicknesses. Test condition is T = 100 °C,  $t_S = 600$  s, and  $V_B = -100$  V.

Fig. 10. Arrhenius plot in the case of stress voltage  $V_{\rm B} = -200$  V, with a stress time of 600 s in the case of different process splits.

Since the charge storage/release mechanisms are linked to the C:GaN layer, a detailed analysis has been performed by changing its thickness and the one of the SL layer.

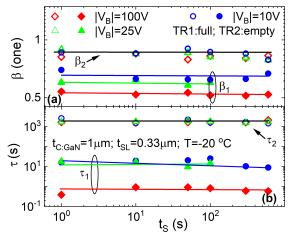

First, a T-dependent analysis has been carried out with  $|V_{\rm B}| = 200$  V and  $t_{\rm s} = 600$  s. The Arrhenius plot in Fig. 10 shows that the activation energies of TR1 and TR2 are unimpacted neither by SL nor by C:GaN thickness, suggesting that the kind of storage/release mechanisms are always the same.

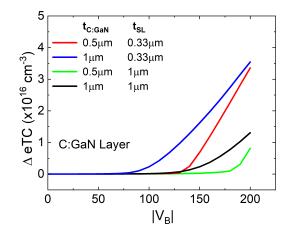

To investigate the role of the two layers on TR1 and TR2, the amplitudes  $A_1$  and  $A_2$  have been analyzed for each split as a function of  $|V_B|$  and reported in Fig. 11(a) and (b), respectively. By focusing on TR1 [Fig. 11(a)], thus on the electron detrapping from carbon-related acceptor states in the C:GaN layer, two trends can be observed: 1) the thinner the C:GaN layer, the smaller the  $A_1$  and 2) the thicker the SL layer, the smaller the  $A_1$ .

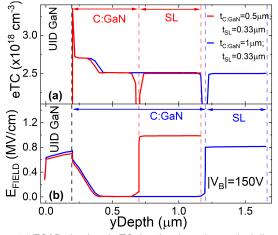

To better understand such experimental evidences, TCAD simulations have been performed by introducing an acceptor states concentration of  $5 \times 10^{18}$  cm<sup>-3</sup> at 0.9 eV from the VB in the C:GaN layer, which is similar to carbon concentration. Fig. 12(a) reports the electron trapped charge (eTC) density along the C:GaN and SL layers in the case of processes featuring the same and different thicknesses for SL ( $t_{SL} = 330$  nm) and C:GaN ( $t_{C:GaN} = 0.5$  and 1  $\mu$ m) layer,

Fig. 11. Stress voltage dependence of Ai in the case of: (a) TR1 and (b) TR2 for different process splits. The test condition is T = 25 °C and  $t_S = 600 \text{ s}$ .

Fig. 12. (a) TCAD simulated eTC density along the vertical direction (*y* cutline) with  $|V_B| = 150$  V for two structures featuring the same  $t_{SL} = 330$  nm and a C:GaN layer thickness of 0.5 (red line) and 1  $\mu$ m (blue line). (b) Corresponding simulated electric field.

respectively. A thicker C:GaN layer leads to a higher electron trapping, which in turn causes a higher  $\Delta R_{ON}$  (A<sub>1</sub>). The reason can be ascribed to a different electric field distribution ruled by a capacitance voltage divider [Fig. 12(b)]. A thicker C:GaN (1  $\mu$ m) gives rise to a smaller capacitance  $C_{C:GaN}$ , whereas the one related to the SL layer  $(C_{SL})$  remains unchanged. The voltage drop across the C:GaN layer ( $V_{C:GaN}$ ) is  $\sim |V_{\rm B}| * C_{\rm SL}/(C_{\rm SL} + C_{\rm C:GaN})$ , whereas the one on the SL layer  $(V_{SL})$  is  $\sim |V_B| * C_{C:GaN}/(C_{SL} + C_{C:GaN})$ . As a result, the smaller the  $C_{C:GaN}$  (thicker C:GaN), the higher the  $V_{C:GaN}$ , and the lower the  $V_{SL}$ . The result of such a divider is a higher electric field in the C:GaN layer [Fig. 12(b)], inducing a higher amount of trapped electrons (higher  $A_1$ ). The opposite effect is obtained by increasing the SL layer thickness, i.e., the thicker the SL, the lower the  $V_{C:GaN}$  and related electric field, the lower the eTC. Fig. 13 shows the simulated  $\triangle$ eTC in the C:GaN layer, calculated with respect to  $V_{\rm B} = 0$  V, for all the process splits. The  $|V_{\rm B}|$ -dependence is qualitatively in agreement with the experiments  $[A_1, \text{Fig. 11(a)}]$ .

Concerning TR2, Fig. 11(b) shows an almost  $V_{\rm B}$ -independent  $A_2$ , except for the low-bias regime where hole accumulation is not saturated yet (see Section V-B), even

Fig. 13. Quasi-stationary simulation of the eTCs density variation ( $\Delta eTC = eTC_{|VB|} - eTC_{|VB|=0V}$ ) as a function of  $|V_B|$  for different process splits.

for relatively long  $t_s$ . In such a case, a thicker SL helps to significantly reduce the electric field along the uid-GaN and C:GaN layers, weakening the electron band-to-band tunneling and giving rise to a smaller  $A_2$  [Fig. 11(b)].

## VII. CONCLUSION

An in-depth analysis of the role of both test conditions and epi-stack buffer of GaN-on-Si devices on the mechanisms inducing  $\Delta R_{ON}$  has been investigated by means of back-gating I-DLTS tests. For the first time, a genetic algorithm has been employed to accurately fit the experiments, which are often the result of two superimposed mechanisms, allowing us to investigate the temperature, stress-bias, and stress-time dependence of the representative parameters (A,  $\beta$ , and  $\tau$ ). According to the state-of-the-art, the first one is ascribed to electron trapping/detrapping in carbon-related acceptor states located in the C:GaN layer, whereas the second one can be associated with hole accumulation at the C:GaN/SL heterointerface.

A further novelty of this work relies on the study of the role of the buffer epi-stack, reporting that both mechanisms do not show dependence on the kind of adopted AlGaN barrier (neither thickness nor Al%) and on the thickness of the AlN nucleation layer. In addition, the second mechanism is almost insensitive also to C:GaN and SL thickness, except for low  $|V_B|$ , whereas the electron trapping in acceptor states is clearly depending on these layer thicknesses, providing useful information for the epi-stack optimization, i.e., vertical scaling down. In particular, a thinner C:GaN layer and a thicker SL layer turn out to be the best choice to attenuate the  $\Delta R_{ON}$  induced by charge storage/release mechanisms, triggered by OFF-state voltage, in the buffer epi-stack.

# REFERENCES

- M. Meneghini, A. Tajalli, P. Moens, A. Banerjee, E. Zanoni, and G. Meneghesso, "Trapping phenomena and degradation mechanisms in GaN-based power HEMTs," *Mater. Sci. Semicond. Process.*, vol. 78, pp. 118–126, May 2018, doi: 10.1016/j.mssp.2017.10.009.

- [2] E. Fabris et al., "Vertical stack reliability of GaN-on-Si buffers for low-voltage applications," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Monterey, CA, USA, Mar. 2021, pp. 1–8, doi: 10.1109/IRPS46558.2021.9405097.

- [3] J.-G. Kim, C. Cho, E. Kim, J. S. Hwang, K.-H. Park, and J.-H. Lee, "High breakdown voltage and low-current dispersion in AlGaN/GaN HEMTs with high-quality AlN buffer layer," *IEEE Trans. Electron Devices*, vol. 68, no. 4, pp. 1513–1517, Apr. 2021, doi: 10.1109/TED.2021.3057000.

- [4] M. Millesimo, N. Posthuma, B. Bakeroot, M. Borga, S. Decoutere, and A. N. Tallarico, "Impact of structural and process variations on the time-dependent OFF-state breakdown of p-GaN power HEMTs," *IEEE Trans. Device Mater. Rel.*, vol. 21, no. 1, pp. 57–63, Mar. 2021, doi: 10.1109/TDMR.2020.3048274.

- [5] T. Kabemura et al., "Enhancement of breakdown voltage in AlGaN/GaN HEMTs: Field plate plus high-k passivation layer and high acceptor density in buffer layer," *IEEE Trans. Electron Device*, vol. 65, no. 9, pp. 3848–3854, Sep. 2018, doi: 10.1109/TED.2018.2857774.

- [6] M. J. Uren et al., "Leaky dielectric' model for the suppression of dynamic R<sub>ON</sub> in carbon-doped AlGaN/GaN HEMTs," *IEEE Trans. Electron Device*, vol. 64, no. 7, pp. 2826–2834, Jul. 2017, doi: 10.1109/TED.2017.2706090.

- [7] M. J. Uren, J. Moreke, and M. Kuball, "Buffer design to minimize current collapse in GaN/AlGaN HFETs," *IEEE Trans. Electron Devices*, vol. 59, no. 12, pp. 3327–3333, Dec. 2012, doi: 10.1109/TED.2012.2216535.

- [8] P. Moens et al., "On the impact of carbon-doping on the dynamic Ron and off-state leakage current of 650 V GaN power devices," in *Proc. IEEE 27th Int. Symp. Power Semiconductor Devices IC's (ISPSD)*, Hong Kong, May 2015, pp. 37–40, doi: 10.1109/ISPSD.2015.7123383.

- [9] M. J. Uren et al., "Intentionally carbon-doped AlGaN/GaN HEMTs: Necessity for vertical leakage paths," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 327–329, Mar. 2014, doi: 10.1109/LED.2013.2297626.

- [10] N. Zagni et al., "'Hole redistribution' model explaining the thermally activated R<sub>ON</sub> stress/recovery transients in carbon-doped AlGaN/GaN power MIS-HEMTs," *IEEE Trans. Electron Devices*, vol. 68, no. 2, pp. 697–703, Feb. 2021, doi: 10.1109/TED.2020.3045683.

- [11] M. J. Uren, M. Cäsar, M. A. Gajda, and M. Kuball, "Buffer transport mechanisms in intentionally carbon doped GaN heterojunction field effect transistors," *Appl. Phys. Lett.*, vol. 104, no. 26, Jun. 2014, Art. no. 263505, doi: 10.1063/1.4885695.

- [12] D. Bisi et al., "Deep-level characterization in GaN HEMTs—Part I: Advantages and limitations of drain current transient measurements," *IEEE Trans. Electron Devices*, vol. 60, no. 10, pp. 3166–3175, Oct. 2013, doi: 10.1109/TED.2013.2279021.

- [13] F. Wach, M. J. Uren, B. Bakeroot, M. Zhao, S. Decoutere, and M. Kuball, "Low field vertical charge transport in the channel and buffer layers of GaN-on-Si high electron mobility transistors," *IEEE Electron Device Lett.*, vol. 41, no. 12, pp. 1754–1757, Dec. 2020, doi: 10.1109/LED.2020.3030341.

- [14] T. Mizutani, T. Okino, K. Kawada, Y. Ohno, S. Kishimoto, and K. Maezawa, "Drain current DLTS of AlGaN/GaN HEMTs," *Phys. Status Solidi A*, vol. 200, no. 1, pp. 195–198, Nov. 2003.

- [15] A. R. Peaker, V. P. Markevich, and J. Coutinho, "Tutorial: Junction spectroscopy techniques and deep-level defects in semiconductors," *J. Appl. Phys.*, vol. 123, no. 16, Apr. 2018, Art. no. 161559, doi: 10.1063/1.5011327.

- [16] D. Bisi et al., "Characterization of high-voltage charge-trapping effects in GaN-based power HEMTs," in *Proc. 44th Eur. Solid State Device Res. Conf. (ESSDERC)*, Venice Lido, Italy, Sep. 2014, pp. 389–392, doi: 10.1109/ESSDERC.2014.6948842.

- [17] C. B. Soh, S. J. Chua, H. F. Lim, D. Z. Chi, W. Liu, and S. Tripathy, "Identification of deep levels in GaN associated with dislocations," *J. Phys., Condens. Matter*, vol. 16, no. 34, pp. 6305–6315, Sep. 2004, doi: 10.1088/0953-8984/16/34/027.

- [18] S. Yang, C. Zhou, Q. Jiang, J. Lu, B. Huang, and K. J. Chen, "Investigation of buffer traps in AlGaN/GaN-on-Si devices by thermally stimulated current spectroscopy and back-gating measurement," *Appl. Phys. Lett.*, vol. 104, no. 1, Jan. 2014, Art. no. 013504, doi: 10.1063/ 1.4861116.

- [19] M. Marso, M. Wolter, P. Javorka, P. Kordoš, and H. Lüth, "Investigation of buffer traps in an AlGaN/GaN/Si high electron mobility transistor by backgating current deep level transient spectroscopy," *Appl. Phys. Lett.*, vol. 82, no. 4, pp. 633–635, Jan. 2003, doi: 10.1063/1.1540239.

- [20] J. Bergsten et al., "Electron trapping in extended defects in microwave AlGaN/GaN HEMTs with carbon-doped buffers," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2446–2453, Jun. 2018, doi: 10.1109/TED.2018.2828410.

- [21] B. Butej, V. Padovan, D. Pogany, G. Pobegen, C. Ostermaier, and C. Koller, "Method to distinguish between buffer and surface trapping in stressed normally-ON GaN GITs using the gate-voltage dependence of recovery time constants," *IEEE Trans. Electron Devices*, vol. 69, no. 6, pp. 3087–3093, Jun. 2022, doi: 10.1109/TED.2022.3170293.

- [22] P. D. Kirchner, W. J. Schaff, G. N. Maracas, L. F. Eastman, T. I. Chappell, and C. M. Ransom, "The analysis of exponential and nonexponential transients in deep-level transient spectroscopy," *J. Appl. Phys.*, vol. 52, no. 11, pp. 6462–6470, Nov. 1981.

- [23] P. Omling, L. Samuelson, and H. G. Grimmeiss, "Deep level transient spectroscopy evaluation of nonexponential transients in semiconductor alloys," *J. Appl. Phys.*, vol. 54, no. 9, pp. 5117-1–5117-6, May 1983.

- [24] R. Vetury, N. Q. Zhang, S. Keller, and U. K. Mishra, "The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs," *IEEE Trans. Electron Device*, vol. 48, no. 3, pp. 560–566, Mar. 2001, doi: 10.1109/16.906451.

- [25] O. Mitrofanov and M. Manfra, "Mechanisms of gate lag in GaN/AlGaN/GaN high electron mobility transistors," *Superlattices Microstruct.*, vol. 34, nos. 1–2, pp. 33–53, Jul. 2003, doi: 10.1016/j.spmi.2003.12.002.

- [26] G. Meneghesso et al., "Trapping phenomena in AlGaN/GaN HEMTS: A study based on pulsed and transient measurements," *Semicond. Sci. Technol.*, vol. 28, no. 7, Jul. 2013, Art. no. 074021, doi: 10.1088/0268-1242/28/7/074021.

- [27] H. Hasegawa and M. Akazawa, "Current collapse transient behavior and its mechanism in submicron-gate AlGaN/GaN heterostructure transistors," J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct. Process., Meas., Phenomena, vol. 27, no. 4, pp. 2048–2054, Jul. 2009, doi: 10.1116/1.3139882.

- [28] J. Enderlein and R. Erdmann, "Fast fitting of multi-exponential decay curves," Opt. Commun., vol. 134, nos. 1–6, pp. 371–378, Jan. 1997.

- [29] R. Storn and K. Price, "Differential evolution-a simple and efficient heuristic for global optimization over continuous spaces," J. Global Optim., vol. 11, no. 4, pp. 341–359, 1997.

- [30] K. Price et al., Differential Evolution: A Practical Approach to Global Optimization. Springer, 2006.

- [31] T. Back et al., *Handbook of Evolutionary Computation*, vol. 97, no. 1. Boca Raton, FL, USA: CRC Press, 1997, p. B1.

- [32] A. Shokrollahi and R. Storn, "Design of efficient erasure codes with differential evolution," in *Proc. IEEE Int. Symp. Inf. Theory*, Jun. 2000, p. 5.

- [33] E. Paolini, G. Liva, and M. Chiani, "Coded slotted ALOHA: A graphbased method for uncoordinated multiple access," *IEEE Trans. Inf. Theory*, vol. 61, no. 12, pp. 6815–6832, Dec. 2015.

- [34] Z.-Q. Fang et al., "Deep centers in a free-standing GaN layer," *Appl. Phys. Lett.*, vol. 78, no. 15, pp. 2178–2180, Apr. 2001, doi: 10.1063/1.1361273.

- [35] D. Kindl et al., "Deep defects in GaN/AlGaN/SiC heterostructures," J. Appl. Phys., vol. 105, no. 9, May 2009, Art. no. 093706, doi: 10.1063/1.3122290.

- [36] A. Armstrong et al., "Impact of carbon on trap states in n-type GaN grown by metalorganic chemical vapor deposition," *Appl. Phys. Lett.*, vol. 84, no. 3, pp. 374–376, Jan. 2004.

- [37] T. Kogiso, T. Narita, H. Yoshida, Y. Tokuda, K. Tomita, and T. Kachi, "Characterization of hole traps in MOVPE-grown p-type GaN layers using low-frequency capacitance deep-level transient spectroscopy," *Jpn. J. Appl. Phys.*, vol. 58, Jun. 2019, Art. no. SCCB36.

- [38] Z. Zhang et al., "Deep traps in nonpolar m-plane GaN grown by ammonia-based molecular beam epitaxy," *Appl. Phys. Lett.*, vol. 100, no. 5, p. 374, Jan. 2012.

- [39] E. Richter et al., "Growth and properties of intentionally carbondoped GaN layers," *Cryst. Res. Technol.*, vol. 55, no. 2, Feb. 2020, Art. no. 1900129, doi: 10.1002/crat.201900129.

- [40] J. L. Lyons et al., "Carbon complexes in highly C-doped GaN," *Phys. Rev. B, Condens. Matter*, vol. 104, no. 7, Aug. 2021, Art. no. 075201.

- [41] U. Honda, Y. Yamada, Y. Tokuda, and K. Shiojima, "Deep levels in n-GaN doped with carbon studied by deep level and minority carrier transient spectroscopies," *Jpn. J. Appl. Phys.*, vol. 51, no. 4S, Apr. 2012, Art. no. 04DF04.

- [42] Q. Deng et al., "Comparison of as-grown and annealed GaN/InGaN: Mg samples," J. Phys. D, Appl. Phys., vol. 44, no. 34, Aug. 2011, Art. no. 345101.

- [43] M. Meneghini et al., "Total suppression of dynamic-R<sub>ON</sub> in AlGaN/GaN-HEMTs through proton irradiation," in *IEDM Tech. Dig.*, San Francisco, CA, USA, Dec. 2017, pp. 33.5.1–33.5.4, doi: 10.1109/IEDM.2017.8268492.

Open Access funding provided by 'Alma Mater Studiorum - Università di Bologna' within the CRUI CARE Agreement